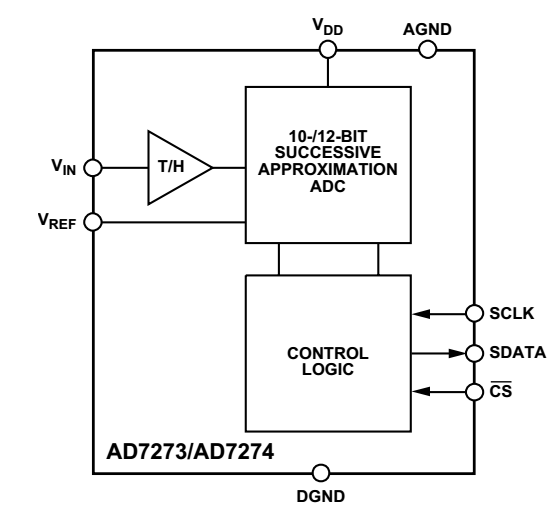

AD7274是一款SPI接口的ADC,最高时钟fsclk为48MHz,最高采样速率为3MSPS。其架构较为简单,逻辑端接口只有SCLK、SDATA、CS三个:

The input signal is sampled on the falling edge of CS, and the conversion is also initiated at this point.

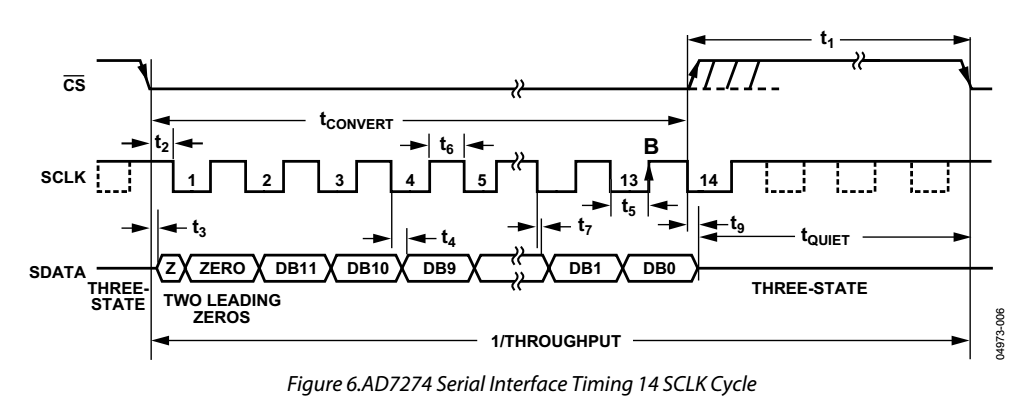

AD7274在CS的下降沿采样,数据输出有14th SCLK和16th SCLK两种,其中14th SCLK可以达到最大的3MSPS采样率,此次设计采用14th SCLK模式。下图为时序图:

可以看出:

1、时钟在空闲的时候应为1,CS拉低后,需要14个时钟的下降沿。

2、CS的下降沿和第一个SCLK的下降沿为t2,t2=6ns min

3、第3个时钟下降沿出采样数据

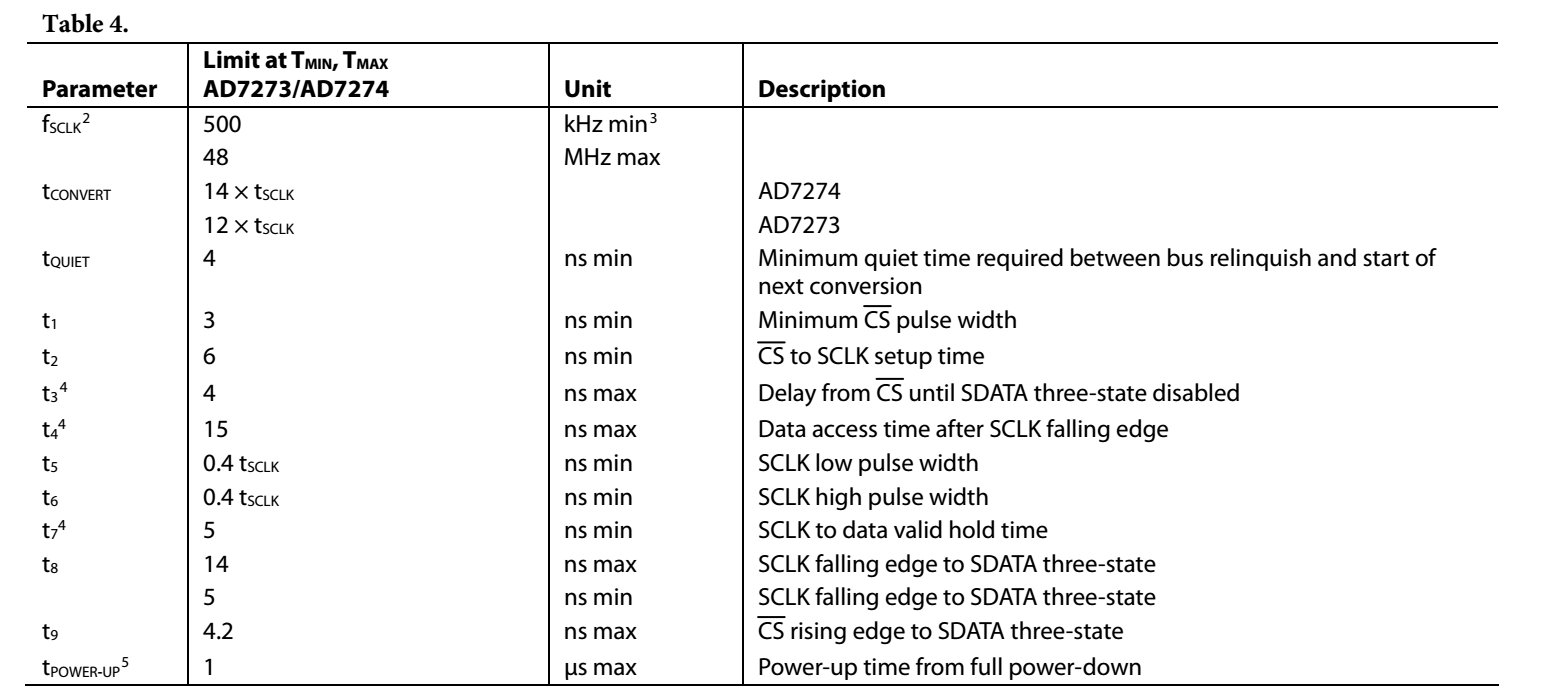

一、时钟设计:

fsclk=48MHz,tsclk = 20.833ns,f4 = fsclk*4 = 192MHz,tf4 =5.208333ns

二、时许设计:

1、总共在f4的时钟频率下循环计数cnt64 = 1-64

2、CS复位拉高,在

cnt64 == 1时,CS <= 0,fsclk <= 1;

cnt64 == 2时,CS <= 0,fsclk <= 1, SDATA = 0;

cnt64 == 3时,CS <= 0,fsclk <= 0, SDATA = 0;

cnt64 == 4时,CS <= 0,fsclk <= 0, SDATA = 0 (sclk 1st falling edge, 1st leading 0);

cnt64 == 5时,CS <= 0,fsclk <= 1, SDATA = 0;

cnt64 == 6时,CS <= 0,fsclk <= 1, SDATA = 0 ( 2nd leading 0);

cnt64 == 7时,CS <= 0,fsclk <= 0, SDATA = 0 ( 2nd leading 0);

cnt64 == 8时,CS <= 0,fsclk <= 0, SDATA = 0 ( sclk 2nd falling edge, 2nd leading 0);

cnt64 == 9时,CS <= 0,fsclk <= 1, SDATA = 0 ( 2nd leading 0);

cnt64 == 10时,CS <= 0,fsclk <= 1, SDATA = DB11;

cnt64 == 11时,CS <= 0,fsclk <= 0, SDATA = DB11;

cnt64 == 12时,CS <= 0,fsclk <= 0, SDATA = DB11;

cnt64 == 13时,CS <= 0,fsclk <= 1, SDATA = DB11;

cnt64 == 14时,CS <= 0,fsclk <= 1, SDATA = DB10;

cnt64 == 15时,CS <= 0,fsclk <= 0, SDATA = DB10;

cnt64 == 16时,CS <= 0,fsclk <= 0, SDATA = DB10;