1 仿真的基础知识

1.1 仿真环境

- TestBench

- 产生测试激励

- 将测试激励施加在待测逻辑上

- 分析待测逻辑结果

- 待测逻辑

1.2 仿真算法

- 基于时间的仿真

- 处理连续的时间,效率较低

- 基于事件的仿真

- 处理电路状态发生变化的情况

- 基于周期的仿真

- 处理时钟的边沿

- 不可用于异步电路

- 相较于基于事件的仿真,时间约束不严格

- 速度快,内存占用小

1.3 仿真工具

- Synopsys:VCS

- Mentor:ModelSim/Questa

- Cadence:Incisive/Xcelium

1.4 仿真的网表

- 基于RTL的仿真:功能仿真

- 基于门级网表的仿真

- 带SDF的门级网表仿真:反标路径上的延迟,更符合实际情况(SDF:Standard Delay Format)

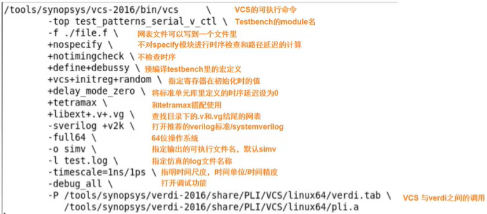

1.5 VCS两步仿真方法

- 编译:Compilation

- 读入网表与标准单元模型,软件建模,生成可执行文件simv(二进制文件)

- 也可以将编译拆分为:analysis&elaborate

- 仿真:Simulation

- 执行可执行文件simv,进行仿真

1.6 VCS两步仿真方法

编译的选项举例:

- +vcs+initreg+random:指定寄存器的初始化值,random为未知态;

- -o simv:指定输出的可执行文件名,默认simv

- -l test.log:指定log文件名

2 Tessent仿真向量的生成

2.1 DC/ASST测试向量

- 产生测试向量:create_patterns

- 写出测试向量:write_patterns

- Verilog格式:用于仿真(自动生成testBench)

- STLI,WGL,ASICII,Binary,etc.

2.2 Memory BIST / Boundary Scan

1.create_patterns_specification:生成特定测试向量的配置

- ICL reading.(ICL文件包含什么信息?作用是什么?)

- Signoff patterns:create_pattern_specification signoff(生成部分测试向量)

- Manufacturing patterns:create_pattern_specification manufacturing(生成用于ATE测试的向量)

2.process_pattern_specification

- Validate_only:验证specification是否正确

- Unprocessed_only:仅对之前未测试的向量进行仿真

- Config_objects:仅对该命令后的器件单元产生测试向量

3.run_testbench_simulations

- set_simulation_library_sources -v 指定仿真模型

- Set_env VCS_HOME/QUESTA_HOME/INCISIVE_HOME xxx 指定仿真工具路径

- Run_testbench_simulations simulator 指定仿真工具

2.3 串/并行仿真向量

1.串行测试向量:write_patterns -serial

- 可以模型ATE实际测试情况

- 仿真时间长

- Pattern sample:set_pattern_filtering -sample N(指定某个某些向量)

2.并行测试向量:write_patterns -parallel

- 将向量直接赋值到寄存器扫描端

- 仿真时间短

2.4仿真向量的内容

以DC parallel pattern为例:

- patterns.v:TestBench

- patterns.v.0.vec:向量文件

- patterns.v.cfg:配置文件

- patterns.v.chain.name:扫描单元的名字

- patterns.v.po.name:Primary output IO