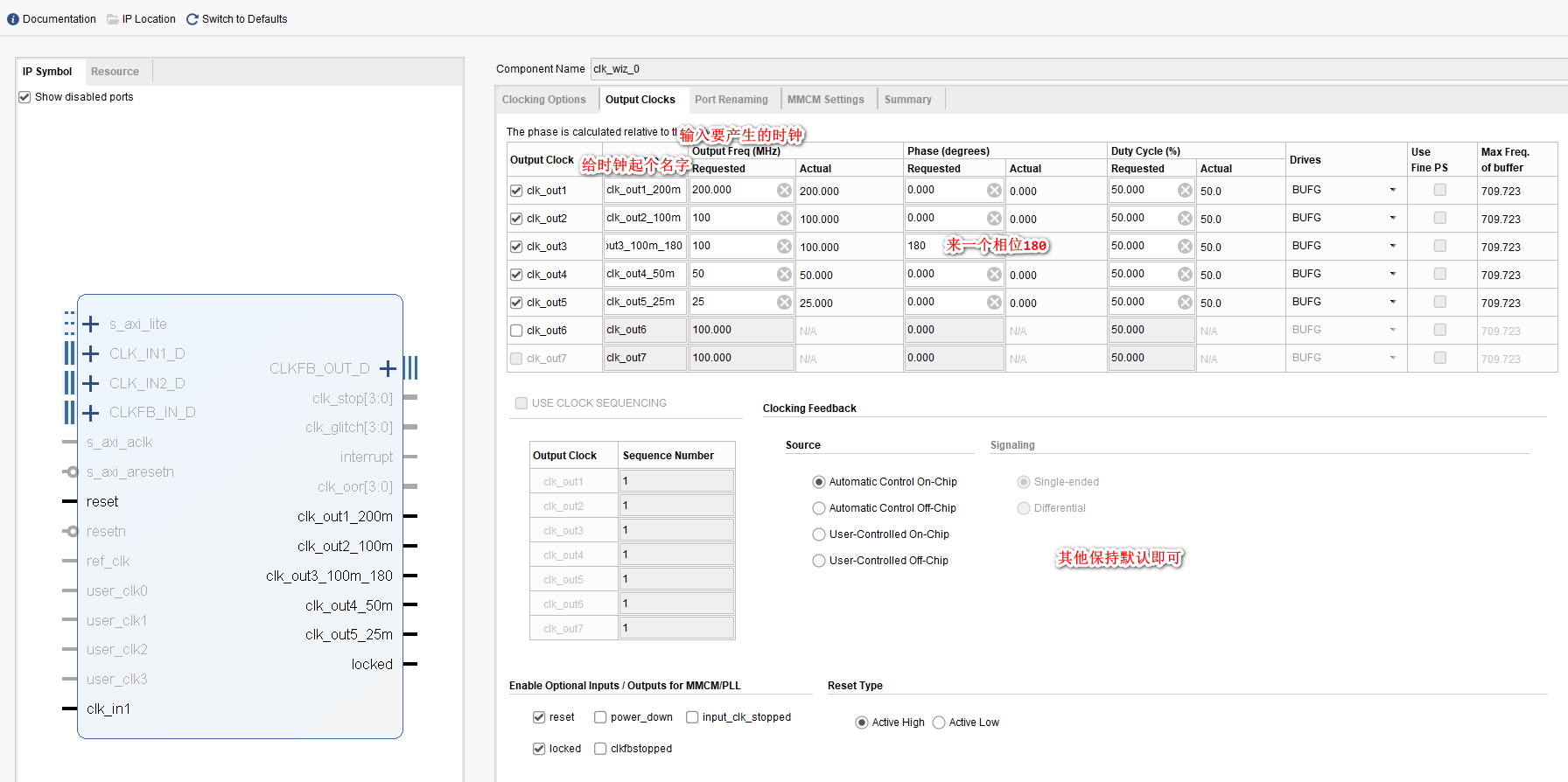

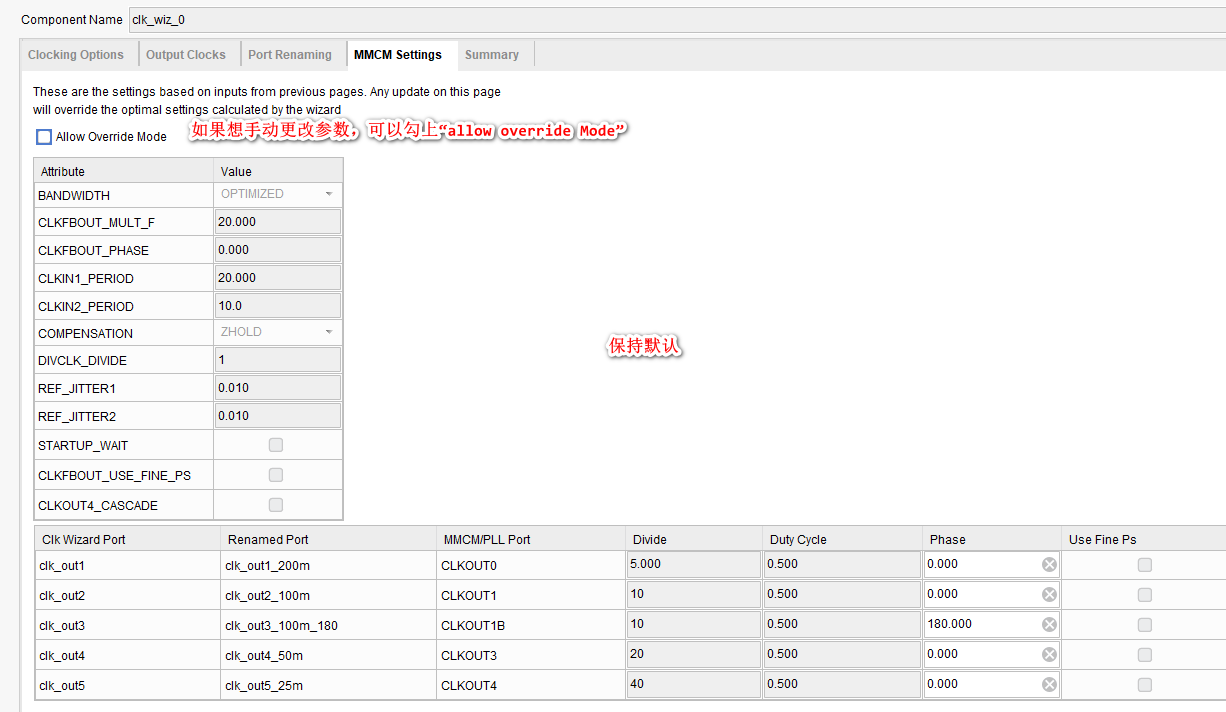

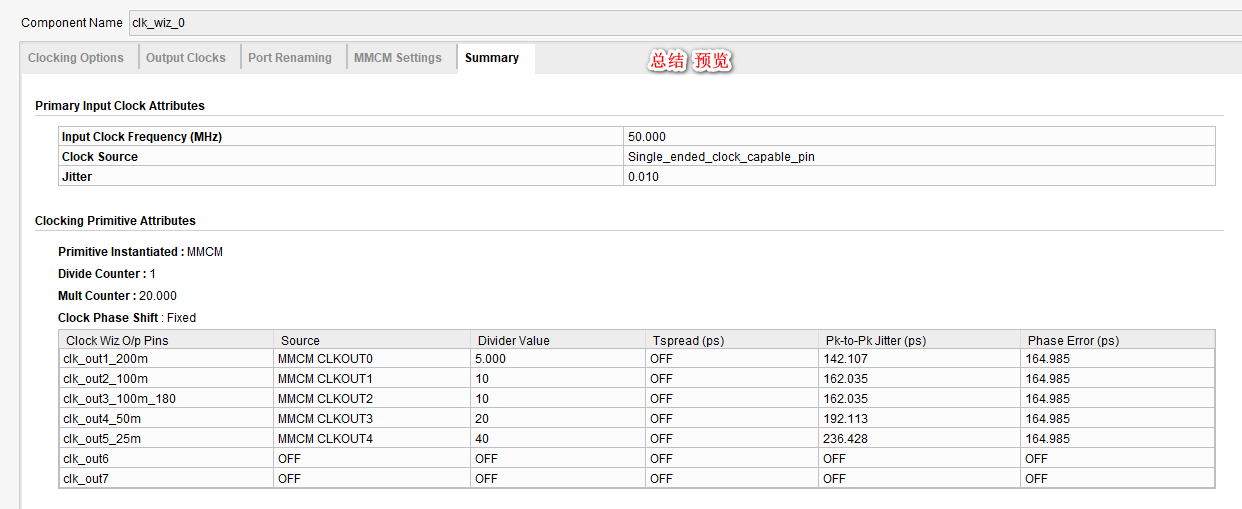

这里选MMCM 进行配置

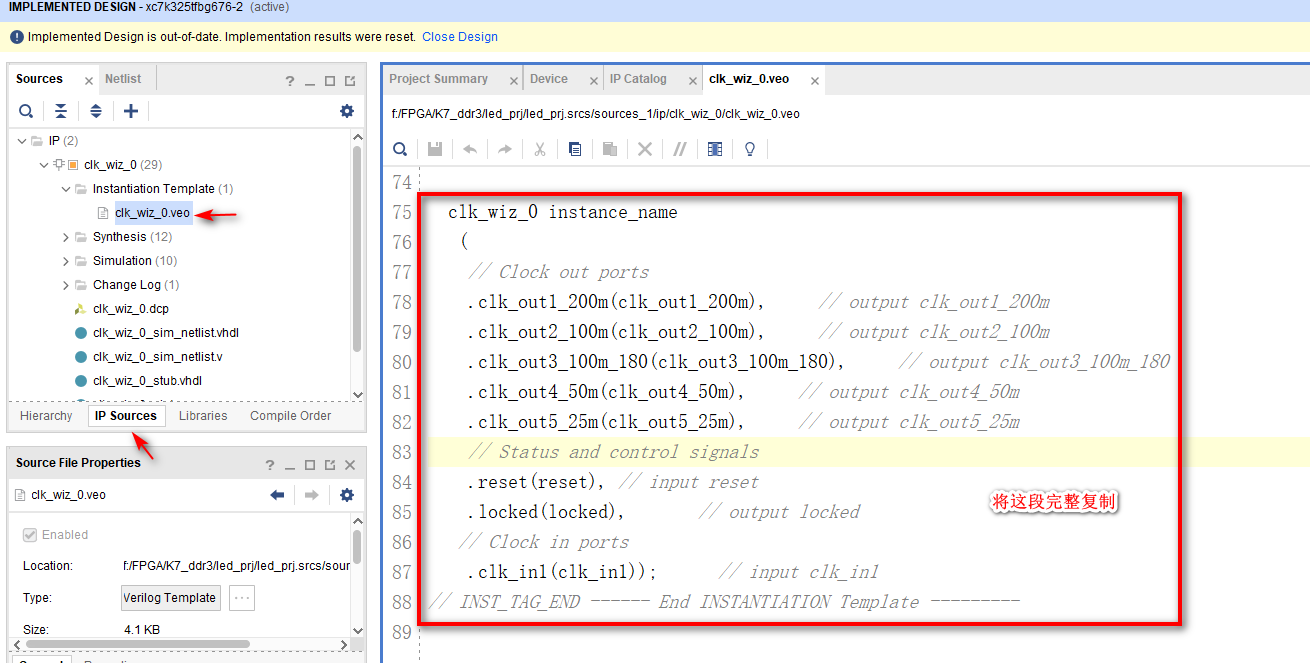

用例化来调用IP,先找到生成IP后,接口例化的地方,软件已经自动例化好,只需将下面这段拷贝到工程文件中进行调用

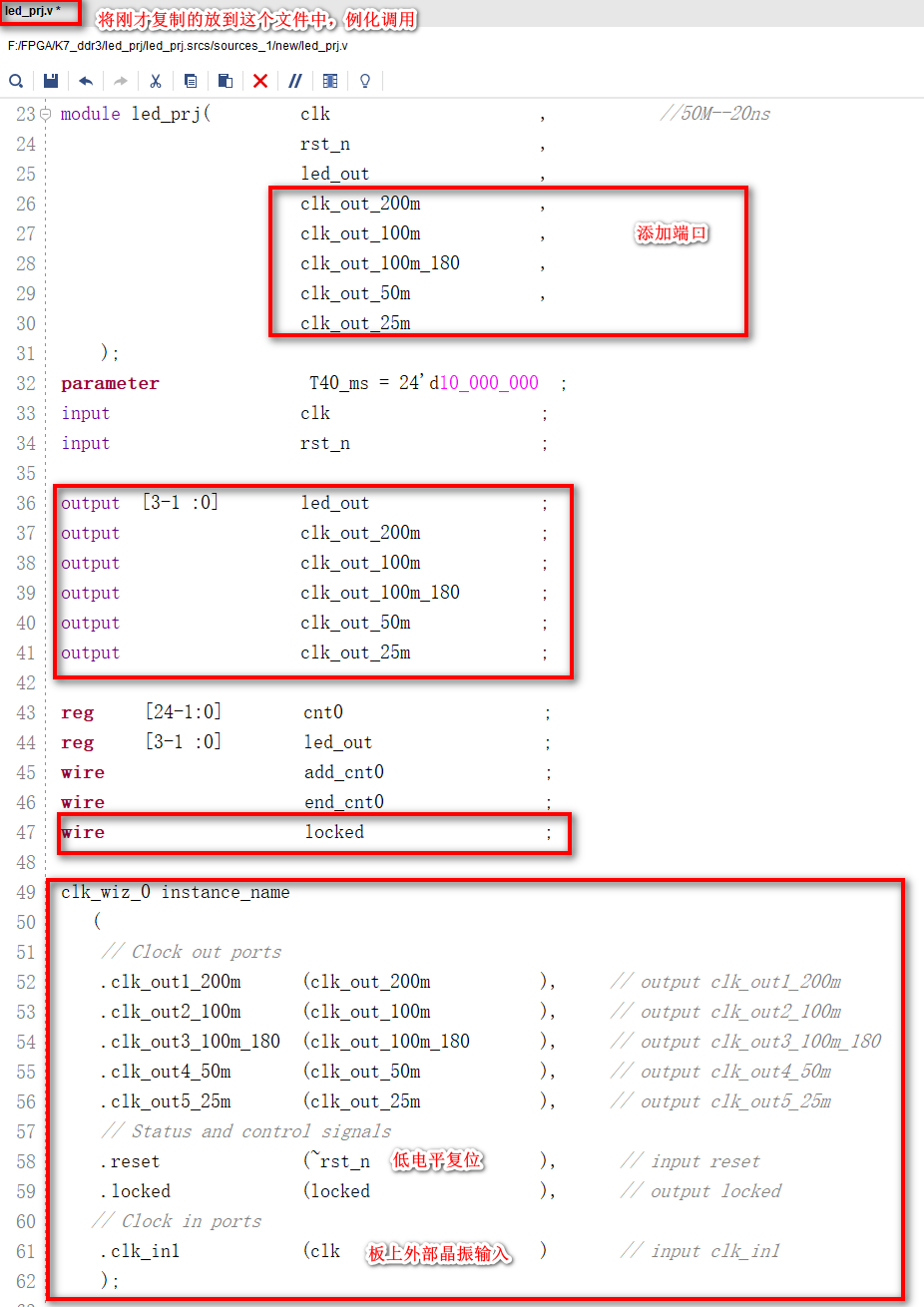

拷贝到led_prj.v文件中

1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 2023/09/03 13:42:40 7 // Design Name: 8 // Module Name: led_prj 9 // Project Name: 10 // Target Devices: 11 // Tool Versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 22 23 module led_prj( clk , //50M--20ns 24 rst_n , 25 led_out , 26 clk_out_200m , 27 clk_out_100m , 28 clk_out_100m_180 , 29 clk_out_50m , 30 clk_out_25m 31 ); 32 33 parameter T40_ms = 24'd10_000_000 ; 34 35 input clk ; 36 input rst_n ; 37 38 output [3-1 :0] led_out ; 39 output clk_out_200m ; 40 output clk_out_100m ; 41 output clk_out_100m_180 ; 42 output clk_out_50m ; 43 output clk_out_25m ; 44 45 reg [24-1:0] cnt0 ; 46 reg [3-1 :0] led_out ; 47 wire add_cnt0 ; 48 wire end_cnt0 ; 49 50 wire locked ; 51 52 always@(posedge clk or negedge rst_n)begin 53 if(!rst_n)begin 54 cnt0 <= 0; 55 end 56 else if(add_cnt0)begin 57 if(end_cnt0)begin 58 cnt0 <= 0; 59 end 60 else begin 61 cnt0 <= cnt0 + 1'b1; 62 end 63 end 64 end 65 66 assign add_cnt0 = 1; 67 assign end_cnt0 = add_cnt0 && cnt0 == T40_ms -1; 68 69 always@(posedge clk or negedge rst_n)begin 70 if(!rst_n)begin 71 led_out <= 3'b001; 72 end 73 else if(end_cnt0)begin 74 led_out <= {led_out[1:0],led_out[2]}; 75 end 76 end 77 78 clk_wiz_0 instance_name 79 ( 80 // Clock out ports 81 .clk_out1_200m (clk_out_200m ), // output clk_out1_200m 82 .clk_out2_100m (clk_out_100m ), // output clk_out2_100m 83 .clk_out3_100m_180 (clk_out_100m_180 ), // output clk_out3_100m_180 84 .clk_out4_50m (clk_out_50m ), // output clk_out4_50m 85 .clk_out5_25m (clk_out_25m ), // output clk_out5_25m 86 // Status and control signals 87 .reset (~rst_n ), // input reset 88 .locked (locked ), // output locked 89 // Clock in ports 90 .clk_in1 (clk ) // input clk_in1 91 ); 92 93 //调用IP中的ILA,在线调试逻辑分析仪,先在工程中例化接口 94 //时钟必须有 95 //需要看什么信号,就添加几个probex,比如 需看cnt0 和 led_out 96 `ifdef ILA_LED_PRJ 97 ila_led_prj u_ila_led_prj( 98 .clk (clk ), 99 .probe0 (cnt0 ), 100 .probe1 (end_cnt0 ), 101 .probe2 (led_out ) 102 ); 103 `endif 104 105 106 107 endmodule

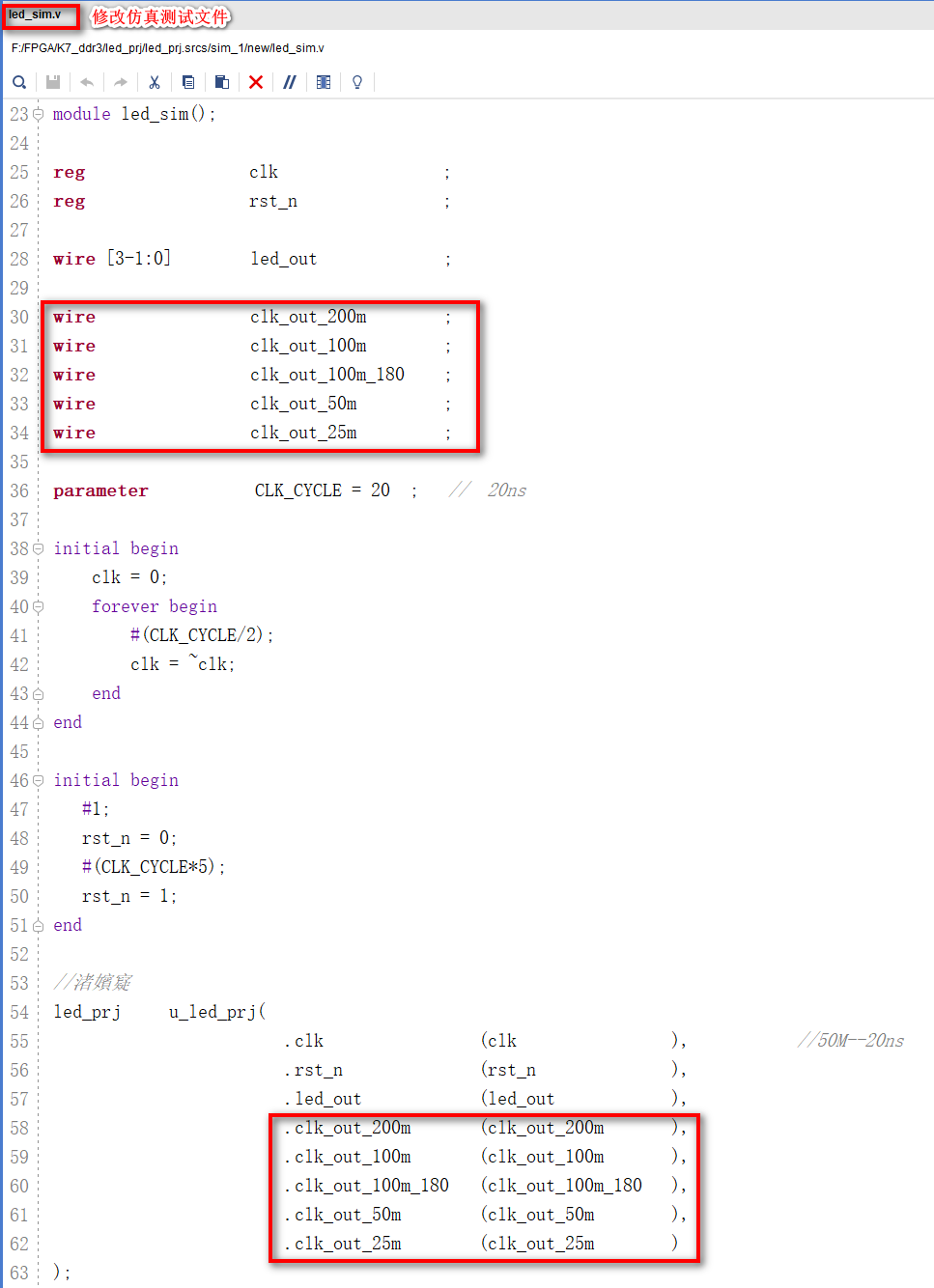

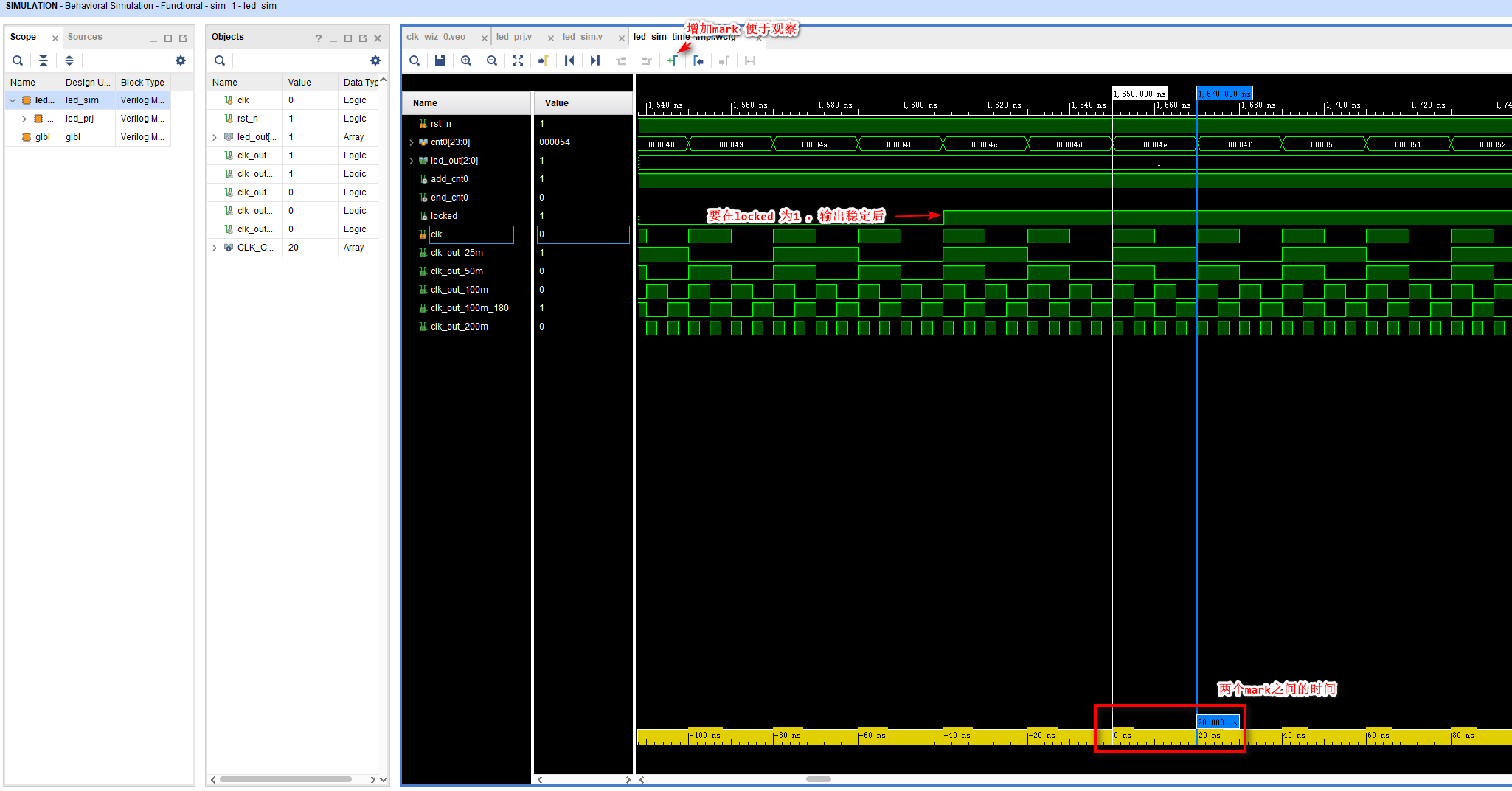

仿真测试文件led_sim.v也需稍微改动下

1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 2023/09/03 21:33:34 7 // Design Name: 8 // Module Name: led_sim 9 // Project Name: 10 // Target Devices: 11 // Tool Versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 22 23 module led_sim(); 24 25 reg clk ; 26 reg rst_n ; 27 28 wire [3-1:0] led_out ; 29 30 wire clk_out_200m ; 31 wire clk_out_100m ; 32 wire clk_out_100m_180 ; 33 wire clk_out_50m ; 34 wire clk_out_25m ; 35 36 parameter CLK_CYCLE = 20 ; // 20ns 37 38 initial begin 39 clk = 0; 40 forever begin 41 #(CLK_CYCLE/2); 42 clk = ~clk; 43 end 44 end 45 46 initial begin 47 #1; 48 rst_n = 0; 49 #(CLK_CYCLE*5); 50 rst_n = 1; 51 end 52 53 //渚嬪寲 54 led_prj u_led_prj( 55 .clk (clk ), //50M--20ns 56 .rst_n (rst_n ), 57 .led_out (led_out ), 58 .clk_out_200m (clk_out_200m ), 59 .clk_out_100m (clk_out_100m ), 60 .clk_out_100m_180 (clk_out_100m_180 ), 61 .clk_out_50m (clk_out_50m ), 62 .clk_out_25m (clk_out_25m ) 63 ); 64 65 endmodule

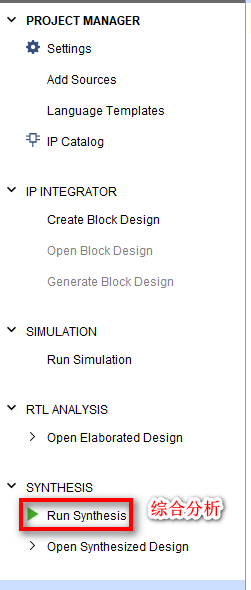

综合分析

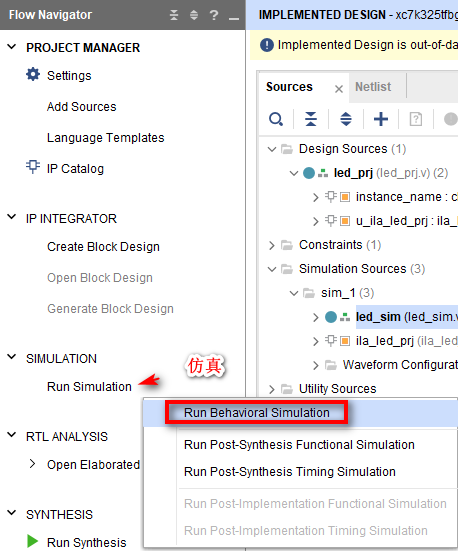

添加信号,观察波形

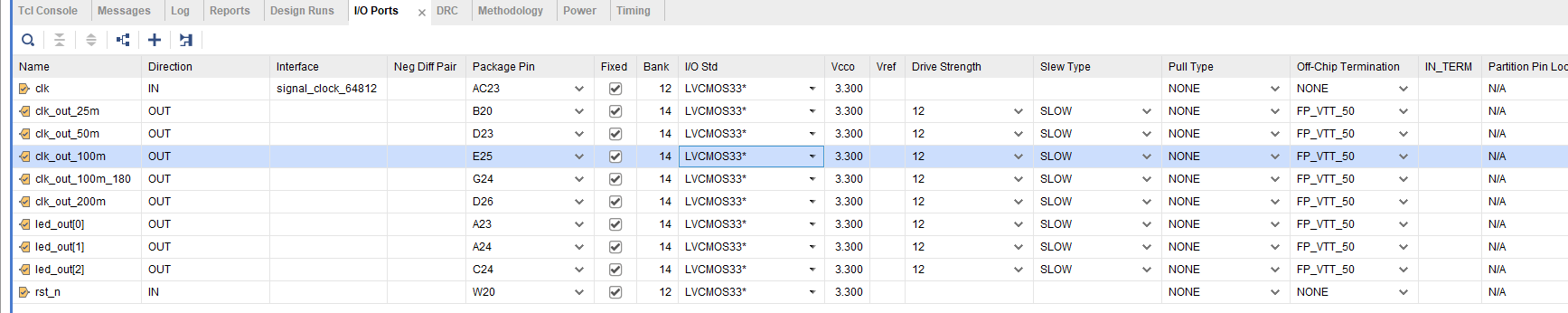

用ILA 在线调试工具抓取波形 ,先把IO分配好

修改ILA 的IP 设置

确认后,直接点生成bit, 进行编译 - 综合 -布局 布线- 生成bit - 下载烧录 ,软件自动调出ILA 波形窗口