简单记一下今天在使用FIFO的过程中的一些注意事项。

【时钟模块】

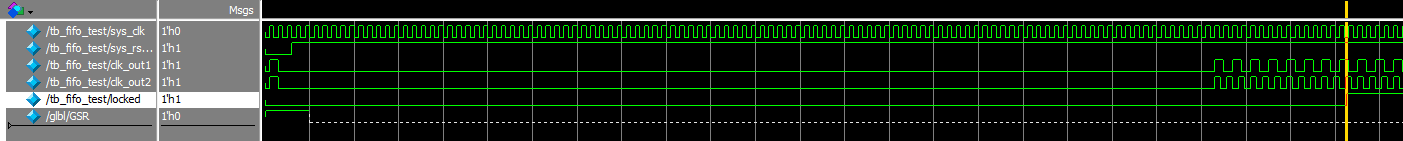

使用时钟模块用于生成FIFO模块的读写时钟,在复位之后时钟模块不能立刻输出时钟,需要等待一段时间(我仿真的时候就想着怎么没数据出来捏)

具体标志为 locked信号拉高

【FIFO模块】

同样的FIFO模块在复位之后也不能立刻工作,需要等待一段时间,

具体的标志信号为 wr_rst_busy 和 rd_rst_busy拉低。

FIFO模块的信号有很多,可以尝试分组记忆,分成读写两种信号。

———— 写 ————

wr_clk (写时钟)

wr_en (写使能)

wr_ack (表明成功写入)

din (写入的数据)

full (fifo写满)

almost_full (fifo快写满了)

wr_data_count (在写时钟域下fifo的计数) ***(fifo full信号的输出是由wr_data_count决定的)

overflow (再写就不礼貌了) 0.0 (严谨一点,包括这次)

———— 读 ————

rd_clk (读时钟)

rd_en (读使能)

valid (表明成功读出)

dout (读出的信号)

empty (fifo读空)

almost_empty (fifo快读空了)

rd_data_count (在读时钟域下fifo的计数) ***(fifo empty信号的输出是由rd_data_count决定的)

underflow (再读就不礼貌了) 0.0 (严谨一点,包括这次)