Verilog 数值处理,在处理减法的时候,需要注意溢出问题。

实例:a*b=c

1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 2023/10/23 23:33:07 7 // Design Name: 8 // Module Name: signed_product 9 // Project Name: 10 // Target Devices: 11 // Tool Versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 22 23 module unsigned_product( 24 input unsigned [7:0] a, 25 input unsigned [7:0] b, 26 output [15:0] product 27 ); 28 assign product=a*b; 29 endmodule

仿真代码:

1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 2023/10/26 23:46:25 7 // Design Name: 8 // Module Name: un_product 9 // Project Name: 10 // Target Devices: 11 // Tool Versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 22 23 module un_product; 24 reg sys_clk; 25 reg unsigned [7:0] a; 26 reg unsigned [7:0] b; 27 wire unsigned [15:0] c; 28 29 initial sys_clk =1; 30 always #1 sys_clk = ~sys_clk; 31 //a = 8'h7f; 32 //b = 8'h2; 33 34 unsigned_product u_product( 35 .a (a), 36 .b (b), 37 .product(c) 38 ); 39 initial begin 40 a=0;b=0; 41 #2 42 a=49;b=73; 43 44 #2 45 a=116;b=108; 46 #2 47 a=61;b=108; 48 #2 49 a=63;b=125; 50 end 51 //assign c = a*b; 52 53 endmodule

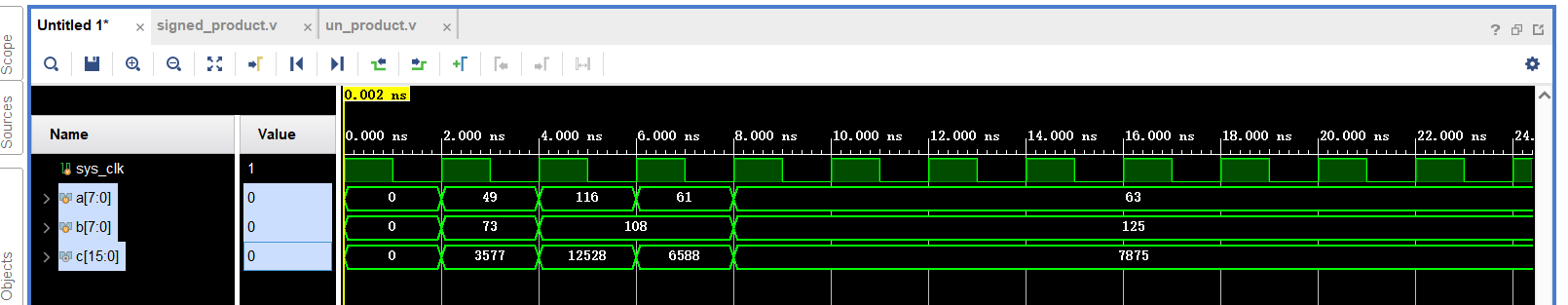

Vivado仿真结果如下:

两个N位相乘 积用N*2+1位来表示。