源码保存成网表(无ip)

新建对应芯片的工程(对应的vivado版本)

添加需要封装的模块文件。

顶层

将需要封装的模块设置为顶层模块。顶层文件一般不包含任何逻辑(封装后仅该文件可见,其他封装成网表文件.edf)

一般包含如下文件。例:

user_axi_uart_v1_3.v //顶层文件

user_axi_uart_v1_3_S00_AXI.v

uartbuf_v3_0.v

fifo_async_d32_8b_ahead_v2_0.v

fifo_async_d32_8b_v2_0.v

tb_uartbuf_v3_0.v //测试文件

总线

需要axi总线时,一般新建ip package时选择,会生成例子,在里边修改。一般情况下使用之前的代码就可以,如果vivado版本变化时可能会导致总线部分信号不识别,就需要新建ip package了。

综合待封装模块

-no_iobuf

vivado综合时会默认将输入输出端口添加buffer缓存,而封装的模块大多都是用在一个大的模块的内部,综合不能添加iobuf,在ISE的综合选 项中有-iobuf选项而在Vivado中该选项是隐藏的,可以在综合设置窗口的Options下面最后一 项 More Options一栏写入“-no_iobuf”,然后综合即可。类似在ISE的综合选项中去掉-iobuf选项。

-flatten_hierarchy

在设置选项的综合设置中选中打平整个设计,防止别人看到模块层次。(settings->Synthesis->Options,-flatten_hierarchy*设置成full)

生成.edif网表文件

打开综合后的设计:在Flow Navigator中点击“Open Synthesis Deisgn”

在TCL Console中输入:“write_edif /path/xx.edif” 。特别注意:路径分隔字符为“/”(得到的网表文件为user_axi_uart_v1_3.edif)

write_edif /path/user_axi_uart_v1_3.edif

在TCL Console中输入

a)导出空壳引脚描述文件: write_verilog -mode synth_stub 自定义目录/da1_gen.v

特别注意:路径分隔字符为“/”

write_verilog -mode synth_stub 自定义目录/da1_gen.v

b) 导出综合后的网表文件:

若不含Xilinx IP则可通过如下命令生成edf文件:

write_edif 盘符目录/ da1_gen.edf

若含Xilinx IP则需通过如下命令生成edf文件:

write_edif -security_mode all 盘符目录/ da1_gen.edf

write_verilog -mode synth_stub uartbuf_v2_3.v

write_edif -security_mode all uartbuf_v2_3.edf

建立wrapper

如果顶层文件包含逻辑,那么需要建立一个与待封装模块同名的.v文件,该文件只描述该模块的接口。

调用

将user_axi_uart_v1_3.v和user_axi_uart_v1_3.edif文件组成文件夹user_axi_uart_v1_3,添加到需要调用的工程中,然后直接对user_axi_uart_v1_3模块进行例化即可。

IP

user_uart_v1_3

xgui

user_axi_uart_v1_3.tcl

component.xml(文件结尾有目录信息和vivado版本信息,可删除)

user_axi_uart.v

user_axi_uart_v1_3.edf(文件结尾有目录信息,可删除)

user_axi_uart_v1_3.v

封装成IP在block中使用(需对应芯片)

以下,未验证

带Xilinx IP的另外一种网表封装方式(不推荐)

上述步骤3后,在tcl命令窗口中执行如下命令:

write_verilog -force abc_stub.v

该命令会将待封装模块中所有源码、IP都写入一个文件中,然后在新工程中仅需添加该文件即可。

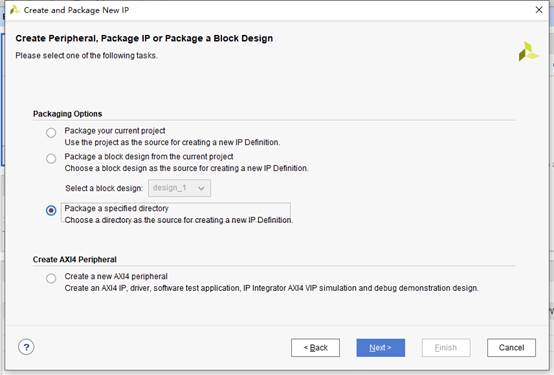

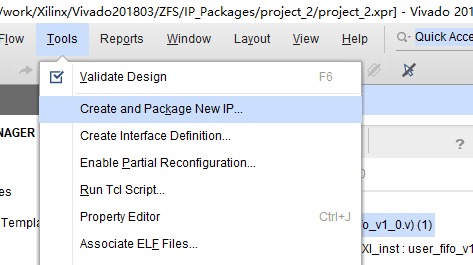

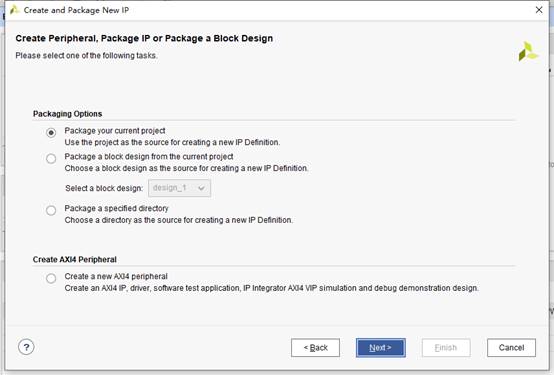

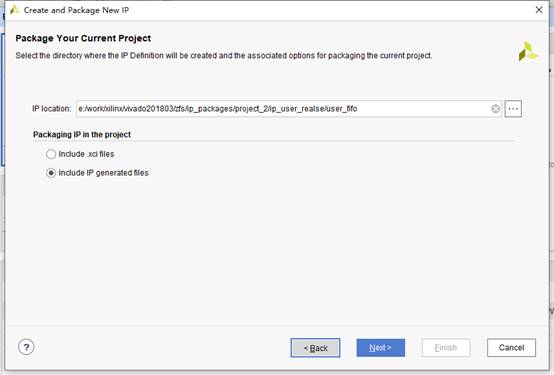

IP package方法一(封装当前工程有fifo)

移除刚才封装的原设计文件,添加 abc_stub.v和abc.edf(注意封装一层)

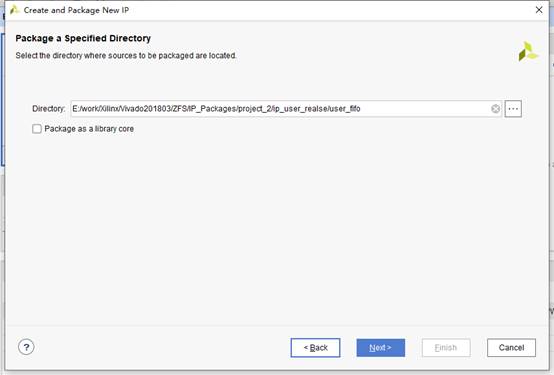

IP package方法二(封装其他目录无fifo)