Verilog 数值处理,在处理减法的时候,需要注意溢出问题。

实例:a*b=c

1 module si_product( 2 input signed [9:0] a, 3 input signed [7:0] b, 4 output signed[17:0] product 5 ); 6 assign product=a*b; 7 endmodule

仿真代码:

1 module si_product_tb; 2 reg sys_clk; 3 reg signed [9:0] a; 4 reg signed [7:0] b; 5 wire signed [17:0] c; 6 7 initial sys_clk =1; 8 always #1 sys_clk = ~sys_clk; 9 //a = 8'h7f; 10 //b = 8'h2; 11 12 si_product si_product( 13 .a (a), 14 .b (b), 15 .product(c) 16 ); 17 initial begin 18 a=0;b=0; 19 #2 20 a=49;b=73; 21 22 #2 23 a=511;b=-128; 24 #2 25 a=61;b=108; 26 #2 27 a=-511;b=128; 28 end 29 endmodule

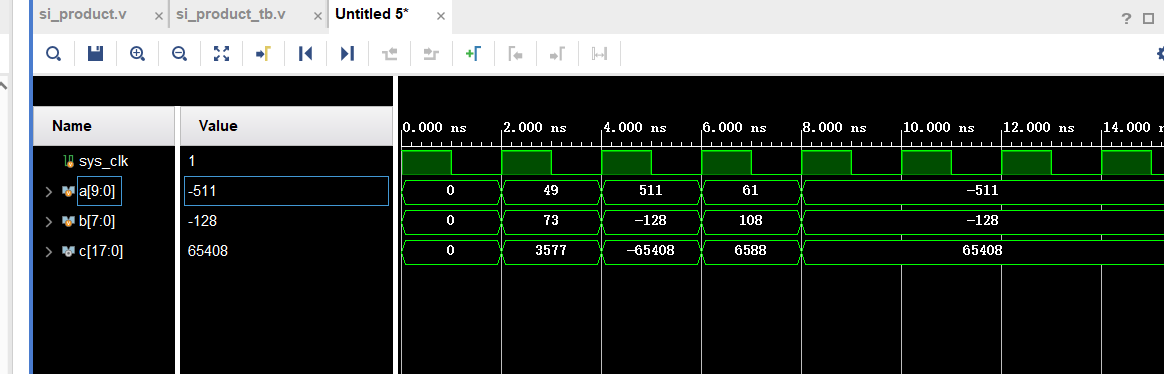

Vivado仿真结果如下:

两个N位*M位相乘 积用N+M+1位来表示。