时钟的属性

时钟偏移(skew):时钟分支信号在到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。

时钟抖动(jitter):相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动。时钟的抖动可以分为随机抖动(Random Jitter)和固有抖动(Deterministic Jitter)。

时钟的偏移和时钟的抖动都影响着时钟网络分枝的延迟差异(相位差异),在Design Compiler里面,我们用时钟的不确定(uncertainty)来表示这两种情况的影响。

时钟的转换时间(transition):时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间。

时钟的延时(latency):时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency)。

Design Compiler中的时钟约束

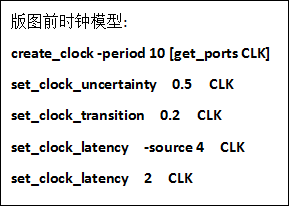

我们用下面的命令建立时钟那几个属性模型:

create_cloclk、set_clock_uncertainty、set_clock_latency、set_clock_transition分别进行时钟的周期、偏移、延时、转换约束。

set_clock_uncertainty:对时钟的偏移和抖动进行建模,也就是对时钟的偏差进行建模。一般情况下,我们只约束建立时间。

set_ clock_ transition:来模拟时钟的转换(transition)时间。默认的上升转换时间为从电压的20%上升至80%的时间,下降的转换时间为从电压的80%下降至20%的时间。

set_clock_latency:进行时钟延时的建模。一般情况下,我们把时钟源延迟(source latency)和时钟网络的延迟(network latency)分开来,因为时钟源延时需要建模,是因为DC是真的不知道这延时是多大,但是对于时钟网络的延迟,DC在布局布线前不知道,但是在布局布线后就可以计算出来时钟网络的延时了,因此在布局布线之后进行综合时,就没有必要对时钟网络进行延时,因此就要把这两个延时分开来进行约束。