1,SDRAM

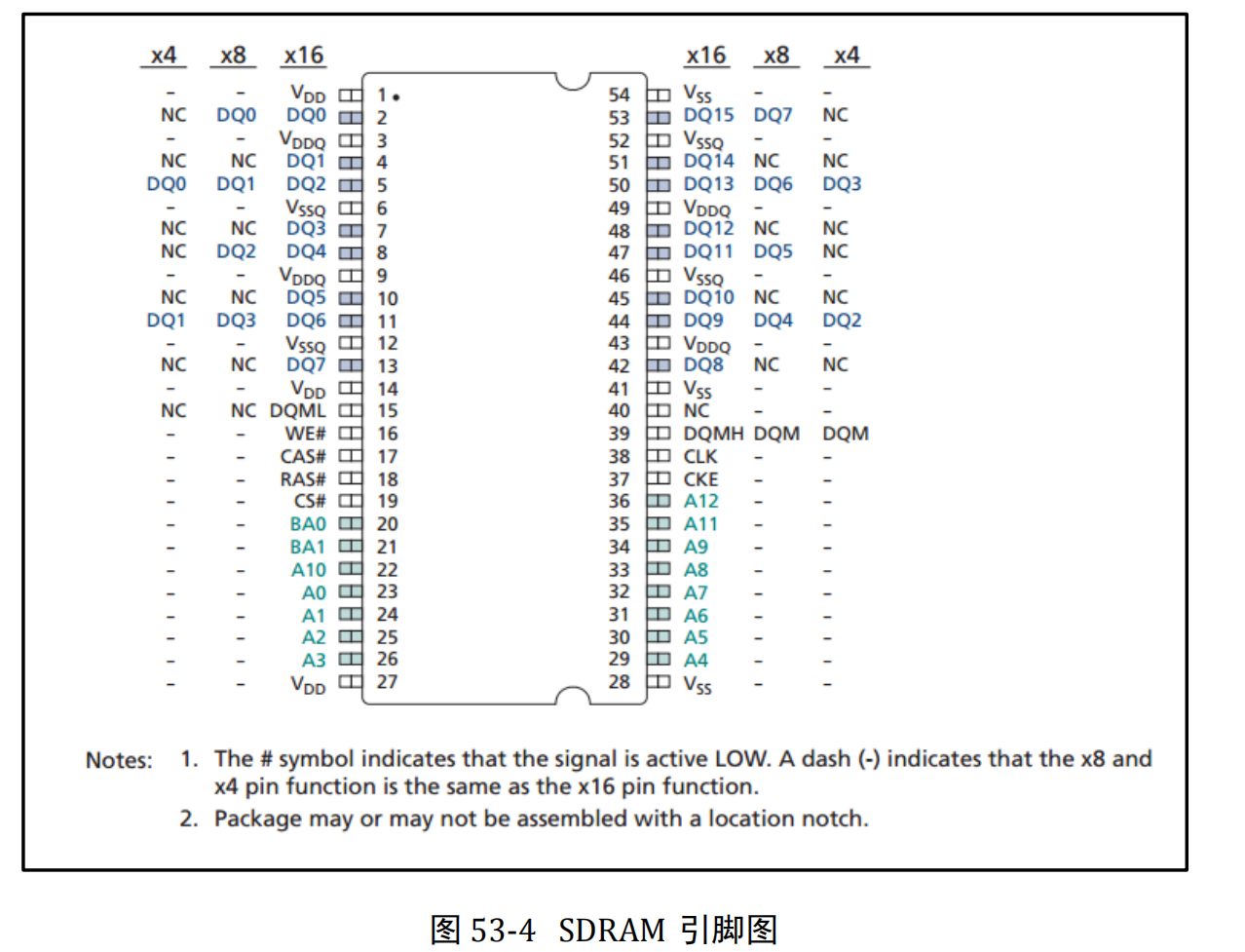

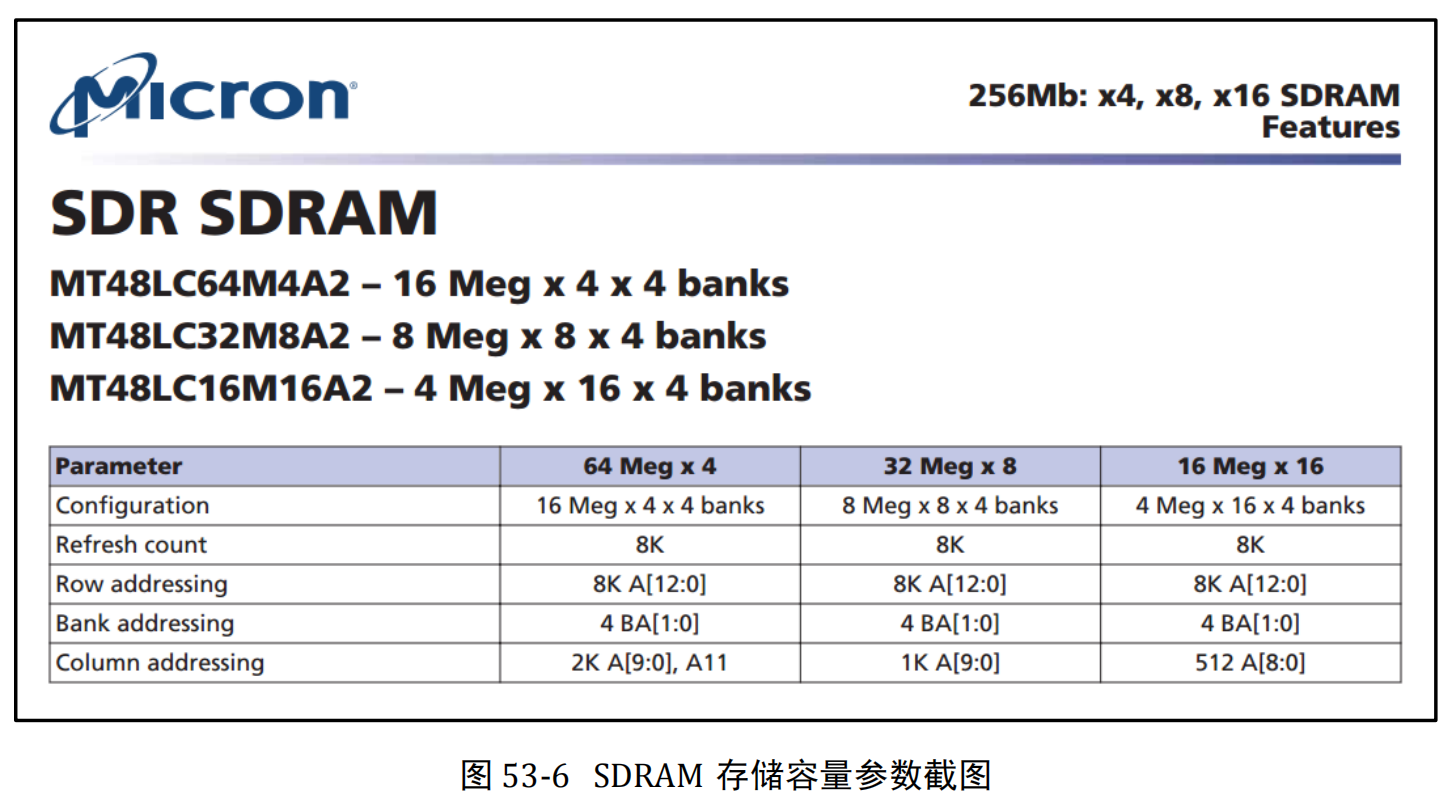

1.1 SDRAM引脚框图

注:x4、x8、x16 分别表示位宽 4bit、8bit、16bit;#符号表示信号为低电平有效;短

划线 - 表示 x8 和 x4 引脚功能与 x16 引脚功能相同。

由于 SDRAM 在容量、位宽以及生产厂家存在差异,所以 SDRAM 在 Bank 地址、地

址总线、数据总线和数据掩码可能存在位宽的差异,但各输入输出管脚的名称和实现功能

并无出入。由图 53-4 已较为详细的展示了不同位宽的 SDRAM 芯片的引脚示意图,针对其

中较为重要的输入输出引脚,我们以镁光公司生产的、容量为 4 Meg x 16 x 4 Banks 的

SDRAM 芯片为例,对其做一下功能介绍。

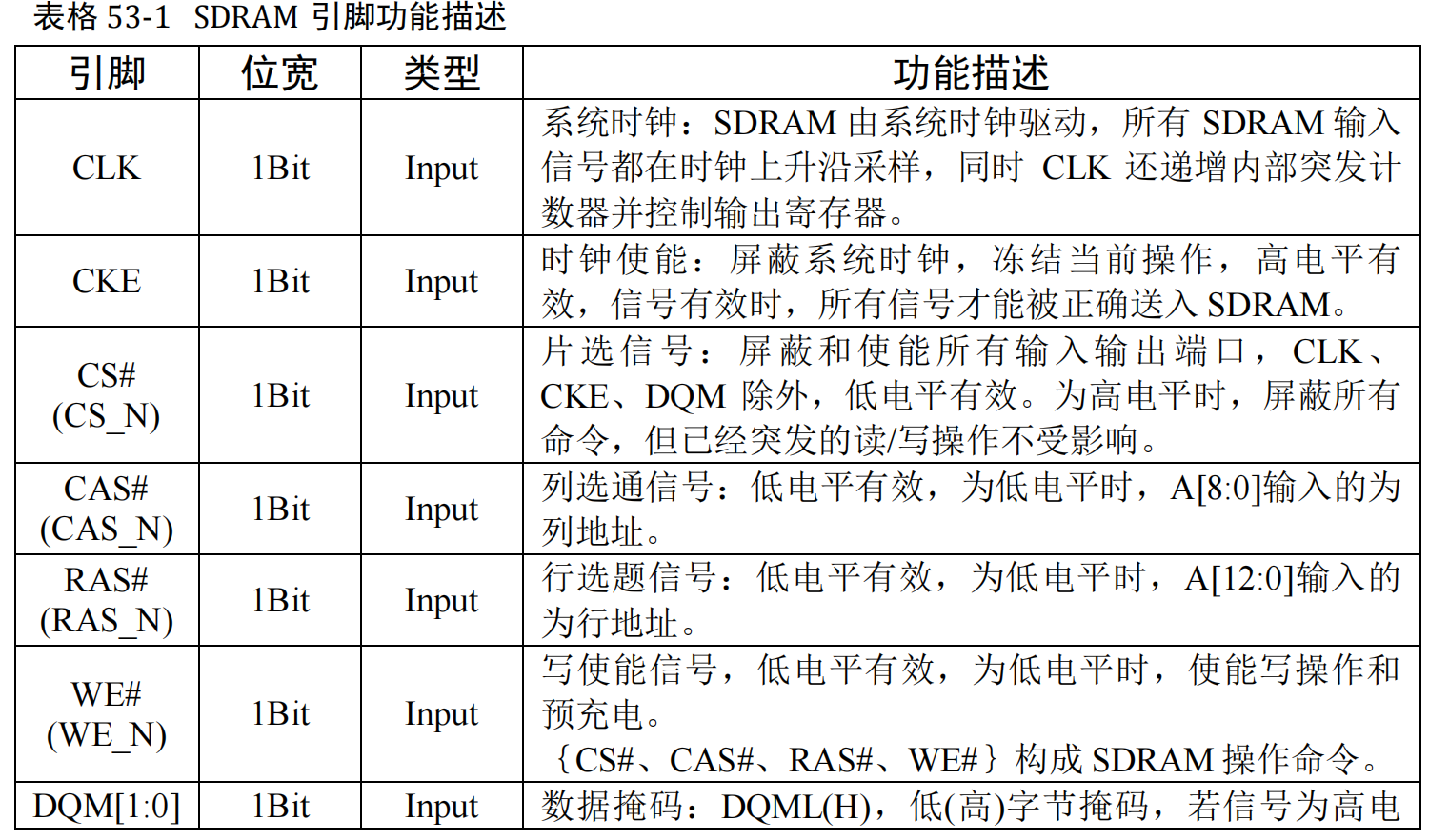

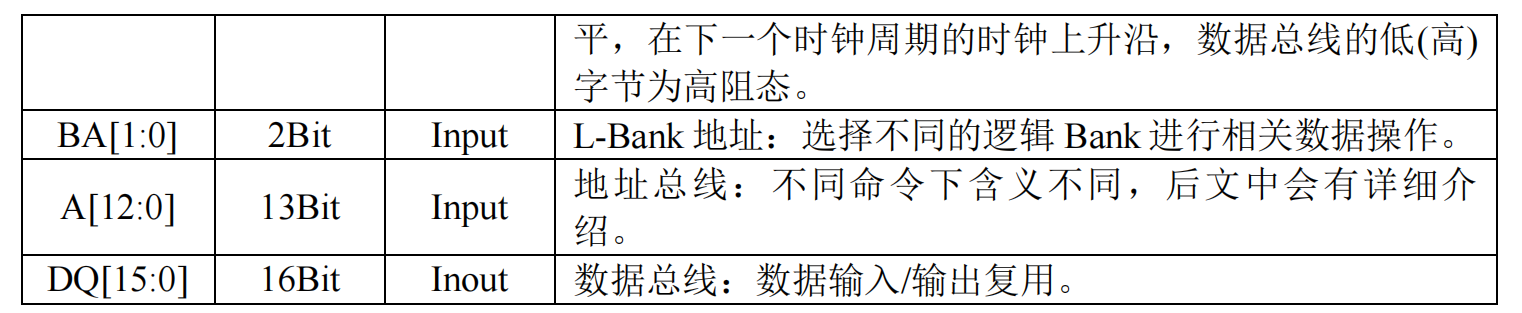

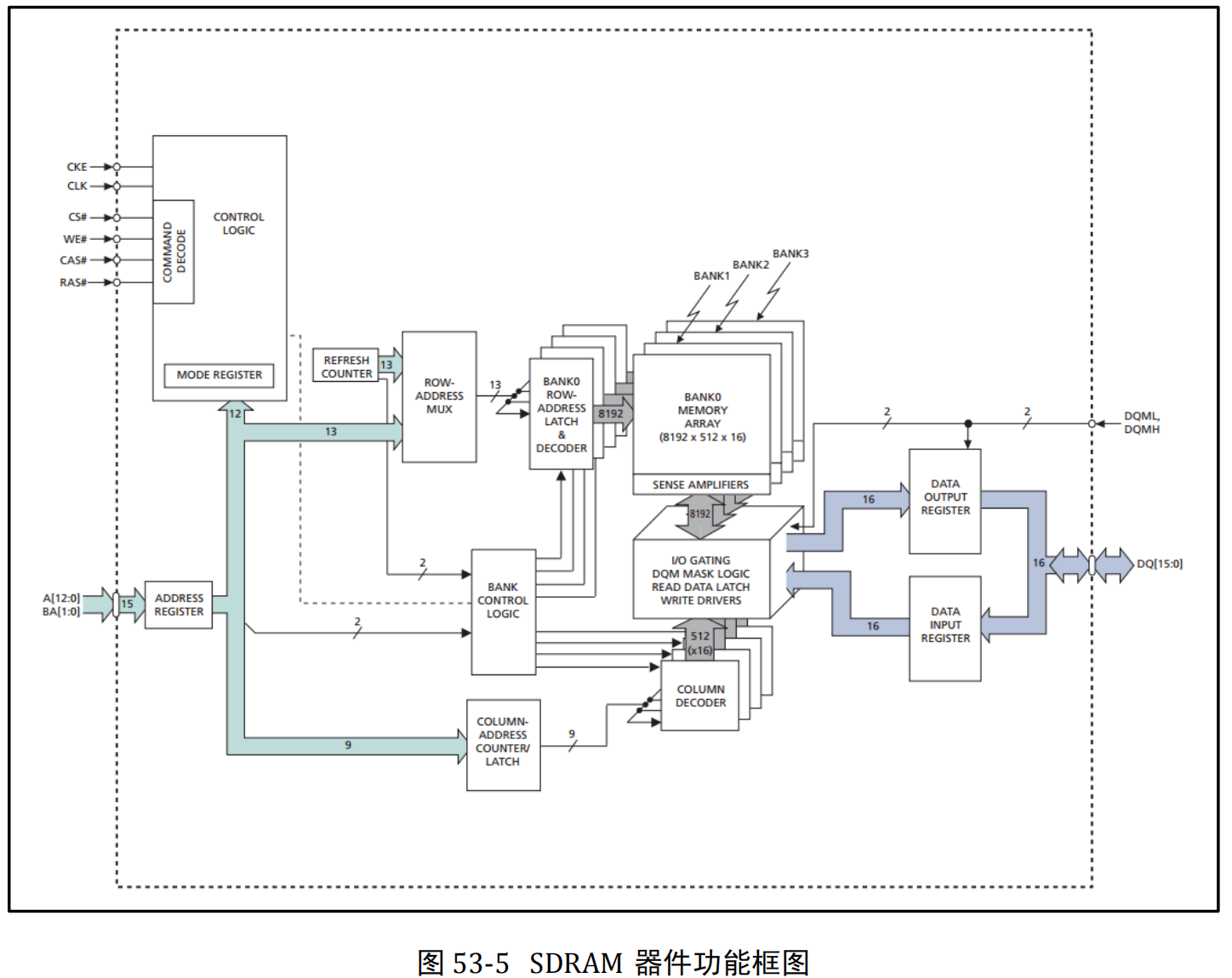

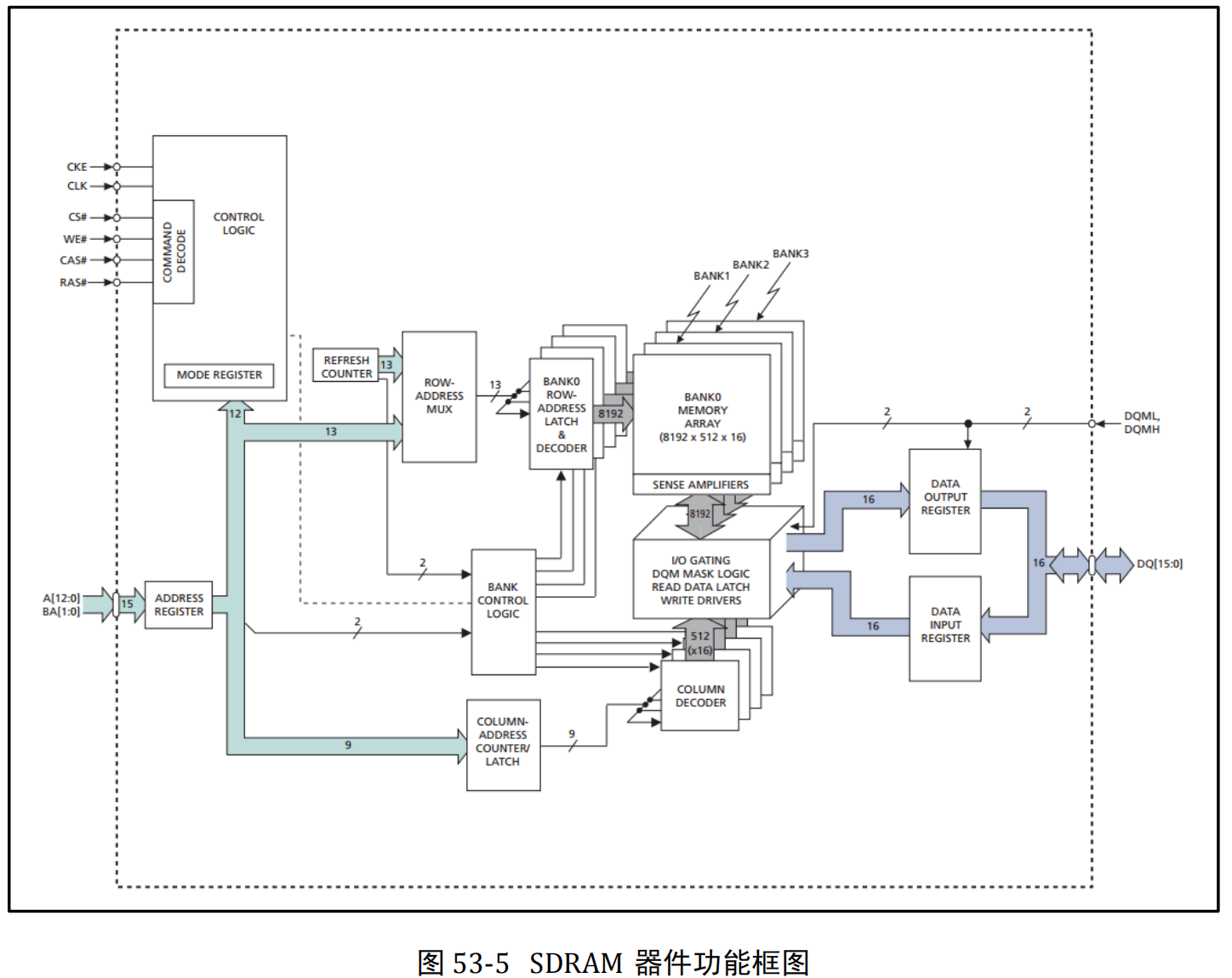

1.2 SDRAM功能框图

SDRAM 内部包含一个逻辑控制单元,内部包含模式寄存器和命令解

码器。外部通过 CS_N、RAC_N、CAS_N、WE_N 以及地址总线向逻辑控制单元输入命

令,命令经过命令解码器进行译码后,将控制参数保存到模式寄存器中,逻辑控制单元进

而控制逻辑运行。

外部通过地址总线输入地址信息,地址信息在逻辑控制单元进行逻辑控制时起到辅助

作用,除此之外,复用的地址总线与 Bank 控制逻辑、行地址复用器、列地址计数锁存

器、列地址解码器等内部器件共同作用,精确选定存储阵列中与行列地址相对应的存储单

元,进而进行数据存取操作。

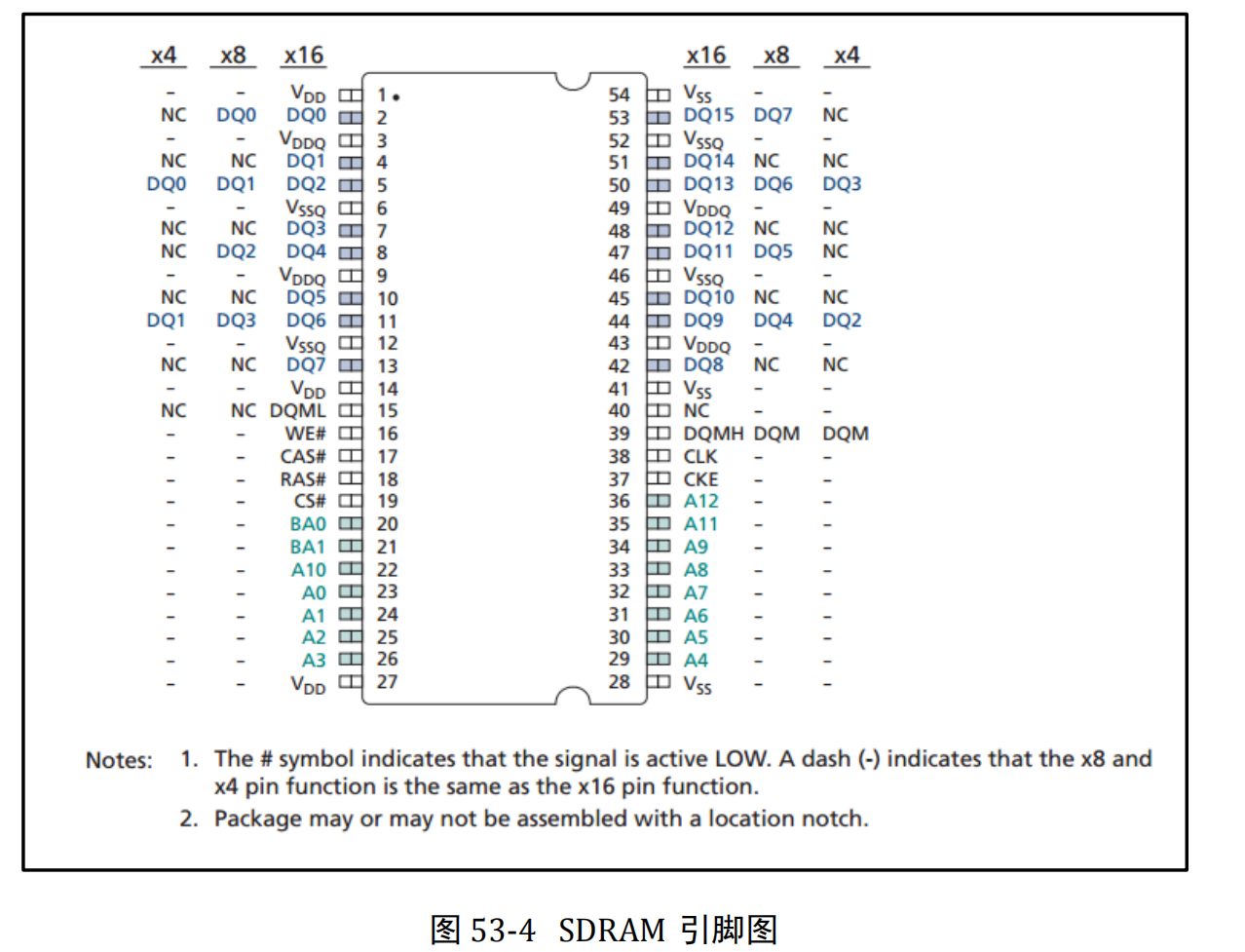

1.3 SDRAM 的存储容量与速度等级

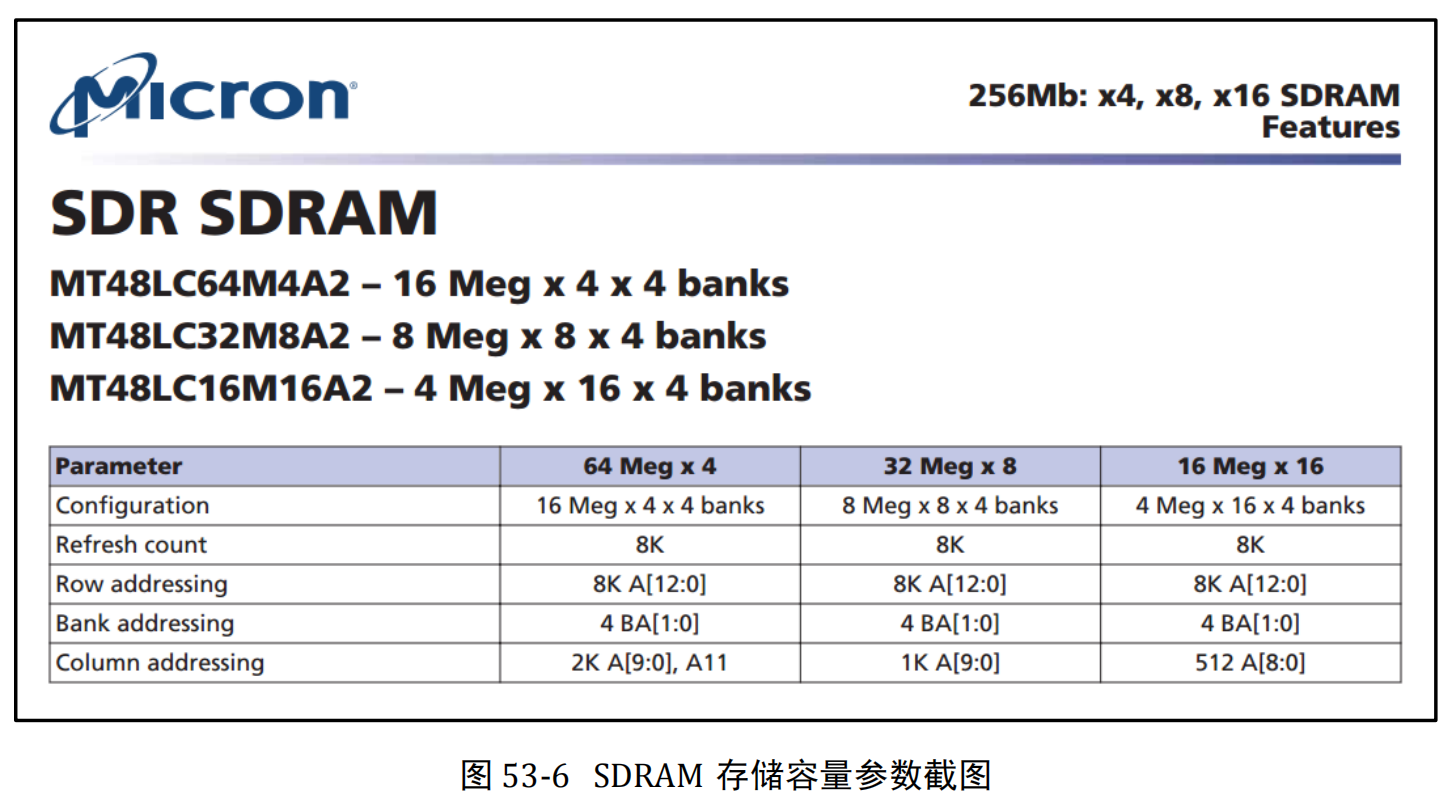

。例“MT48LC16M16A2”,由图可知,“Micron”“MT48LC16M16A2”分别表示此

SDRAM 芯片的生产商和产品型号。“4Meg × 16 × 4Banks”才是表示 SDRAM 存储容量

的具体参数,其中“4Meg”表示单个 L-Bank 包含的存储单元的个数,计算方法为单个存

储阵列行地址数和列地址数的乘积,以此芯片为例,行地址总线为 A0-A12,行地址位宽为

13 位,行地址数为 8192 (2^13)行,列地址位宽为 9 位,列地址数为 512(2^9)列,单个 L�

Bank 中包含的存储单元个数为行地址数(8192)与列地址数(512)相乘,乘积为 4M(8192 ×

512 = 4194306); “16”表示数据位宽,即每个存储单元存储数据的 bit 数;4Meg 与 16 相

乘表示单个 L-Bank 中可存储的 Bit 数;“4BANKS”表示一片 SDRAM 中包含的 L-Bank

个数,此 SDRAM 芯片包含 4 个 L-Bank;由此可得 SDRAM 芯片的存储容量为:

256MBit(4Meg × 16 × 4BANKS)。

容量计算方法可简化为:

存储容量(Bit) = L-Bank 存储单元数 ×数据位宽(Bit) × L-Bank 个数

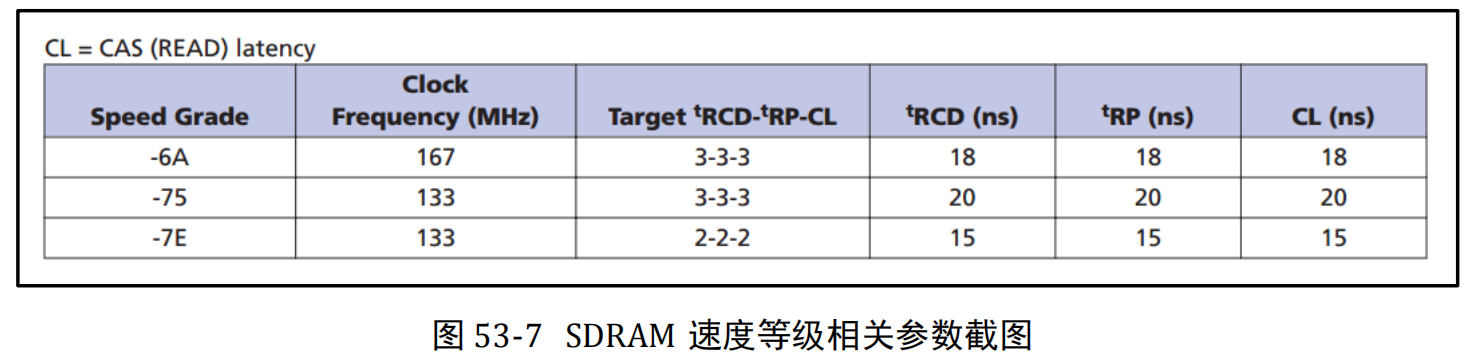

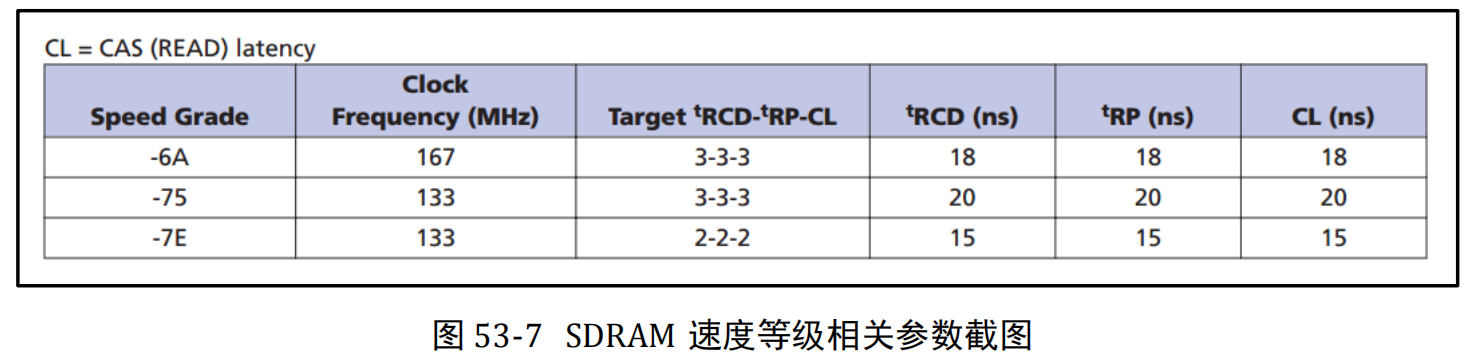

时钟频率(Clock Frequency),单位

MHz,所列举的具体参数为 SDRAM 正常工作的最高时钟频率,SDRAM 工作时只能等于

或低于这一时钟频率;tRCD 表示写入自激活命令到开始进行数据读写,中间所需的等待时

间,列举的数值表示等待时间的最小值,单位为 ns; tRP 表示自预充电指令写入到预充电

完成所需的等待时间,列举的数值表示等待时间的最小值,单位为 ns;CL(CAS(READ)

latency)列选通潜伏期,表示自数据读指令写入到第一个有效数据输出所需等待时间,单位

ns;Target tRCD-tRP-CL 表示最大工作频率下,tRCD、tRP、CL 等待的最小时钟周期数。

1.4 基本操作与时序

1.4.1 芯片初始化(MRS)

设定BL数值,读写操作模式(突发与否),突发传输模式(顺序传输,交错传输)

1.4.2 行选址(Row),使之处于活动状态

片选与L-Bank的定址同时进行,RAS(行地址选通脉冲)也处于有效状态。此时An地址线则发送具体的行地址

1.4.3 列选址与读写命令

列寻址地址线与行寻址地址线共用,但CAS可以区分行与列寻址的不同。

列选址时,CAS(列地址选通脉冲)与RAS命令之间必须有一个间隔,间隔为tRCD,可以理解为行选通周期,一般以时钟周期为单位,比如tRCD=2,代表延迟周期为两个时钟周期。

读写命令与列寻址信号同时发出,WE#无效时,为读取命令。

1.4.4 读操作

数据通过数据IO通道(DQ)输出到内存总线上;

CAS瞬间到达存储单元,但存储体中晶体管的反应时间会造成数据不可能与CAS在一个上升沿触发;从CAS与读取命令发出的第一笔数据输出的时间称为CL(CAS潜伏期),是时钟周期数。

数据在数据总线上,输出之前要经过S-AMP通道对数据进行放大,这段时间称为tAC;tAC的时间包括在CL时间内。如下图

1.4.5 写操作

写入的操作也是在tRCD后,但此时没有CL;WE#此时为有效状态。

写操作的写入数据可以与CAS同时发送,也就是说写入延迟为0。但是选通三极管与电容充电必须有一段时间,所以真正的写入需要一定周期:tWR,这个操作也被称为写回。

1.4.6突发长(burst):同一行相邻的存储单元连续进行

突发传输技术产生原因:当要连续读写时,对当前存储单元的下一个单元寻址,不断发送读写命令与列寻址命令(行地址不变),占用大量内存控制资源。所以burst技术应运而生。

burst技术只要指定起始列地址与突发长度,内存就会依次自动对后面相应数量的存储单元进行读写操作而不再需要控制器连续地提供列地址。

BL的数值,不能随便设置,在MRS阶段就要对BL设置,一般是定死的,常见设置为4和8。

1.4.7 预充电

对一行读写操作后,关闭现有工作行,准备打开新行的操作就是预充电。

在发出预充电命令后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行,这个间隔称为tRP(precharge period)

1.4.8 刷新

DRAM要不断进行刷新才能保留住数据。

预充电是对一个或所有L-Bank中的工作行操作,并且是不定期的,有固定周期(64ms);刷新过程中,所有L-Bank都停止工作,等待刷新结束后,才能进入正常的工作状态。

1.4.9 数据掩码

为了屏蔽不需要的数据,采用数据掩码(DQM)技术;

在读取时,被屏蔽的数据仍然会从存储体中传出,只是在“掩码逻辑单元”处被屏蔽。