1. 概述

AMBA架构的SoC,一般包括用于high-performance的system bus-AHB与low-power的peripheral bus-APB。System bus负责core与DMA controller、on-chip memory以及其他interface或需要high bandwidth的元件。而peripheral bus则用于连接off-chip外设,其协议相比AHB较为简单,与AHB之间通过Brigde相连。典型AMBA架构如图1.1:

图1.1

2. AHB简介

AHB(Advanced High-Performance Bus)用作on-chip system bus,其主要特性包括:

- 单时钟沿触发

- 非三态(无高阻态)

- burst传输

- split事务

- 支持多master

2.1 Overview

AHB System是由Master、Slave以及Infrastructure三部分组成。所有transfer都由master发出,由slave负责回应。而infrastructure则是由arbiter、master to slave multiplexor、slave to master multiplexor、decoder、dummy slave以及dummy master所组成。

NOTE:AHB2相比后续的AHB3_lite以及AHB5保留了arbiter并支持split、retry传输。

AHB的arbiter主要用于仲裁多路master。decoder则负责地址解码,并且包含HSELx信号用来选择要回应传输的slave。而两个多路选择器负责bus的传输路线,如下图2.1。

图 2.1

bus信号可以分为clock、arbitration、address、control、write data、read data以及reasponse七种。除了clock和arbitration信号外,其他信号均会经过多路选择器。

下表为AHB信号及其用途:

| Name | Source | Description |

| HCLK | Clock | 总线时钟 |

| HRESETn | Reset controller | 低复位 |

| HADDR[31:0] | Master | 32位地址总线 |

| HTRANS[1:0] | Master | 传输类型:IDLE、BUSY、NONSEQ、SEQ |

| HWRITE | Master | 高写低读 |

| HSIZE[2:0] | Master | 传输size可配 |

| HBURST[2:0] | Master | 突发类型:SINGLE、INCR、INCR4、INCR8、INCR16、WRAP4、WRAP8、WRAP16 |

| HPORT[3:0] | Master | 提供总线访问的附加信息,给那些需要执行某种保护级别的模块使用。 |

| HWDATA[31:0] | Master | 写数据 |

| HSELx | Decoder | 每个AHB slave都有独立的HSELx信号用来表示当前传输是否打算传给选中的slave |

| HRDATA[31:0] | Slave | 读数据 |

| HREADY | Slave | 高传输有效,低传输扩展 |

| HRESP[1:0] | Slave | 传输响应信号:OKEY、ERROR、RETRY以及SPLIT |

| HBUSREQx | Master | bus请求:向arbiter发出请求控制总线的信号 |

| HLOCKx | Master | 向arbiter提示正执行不可分割的传输 |

| HGRANTx | Arbiter | bus授予:表示主机x目前是优先级最高的主机 |

| HMASTER[3:0] | Arbiter | 主机id标识 |

|

HMASTERLOCK |

Arbiter | 向slave发出:锁定当前传输队列 |

| HSPLITx[15:0] | Slave | slave向arbiter指示哪个master可以完成剩余的split传输 |

图 2.2

上图2.2展现了AHB大致的互连情况,其中省略的部分有:

- 各种control信号(HBURST,HTRANS等)的连接,其连线与HADDR一致。

- Master与Arbiter之间的Request/Grant信号。

- Decoder与各个slave之间的selection信号

- control mux的输出有部分control信号会接到Arbiter(HTRANS/HBURST)。

- Response信号(HREADY、HRESP)的mux

- Arbiter会输出HMASTER信号接到master-to-slave 多路选择器,用作selection信号。

2.2 AHB传输

2.2.1 传输概括

- Master可以在任何周期向Arbiter发送HBUSREQ请求信号,master在传输开始前必须被HGRANT授予访问bus;

- 被授予访问bus的master驱动addr、control信号开始发起一次传输;

- 写数据通道HWDATA同来将数据从master传输至slave,读数据HRDATA用来将数据从slave返回至master;

- 一次传输包括:一个addr和control周期以及一个或多个data周期;

- 传输过程中slave通过HRESP返回状态:OKAY、ERROR、RETRY和SPLIT。

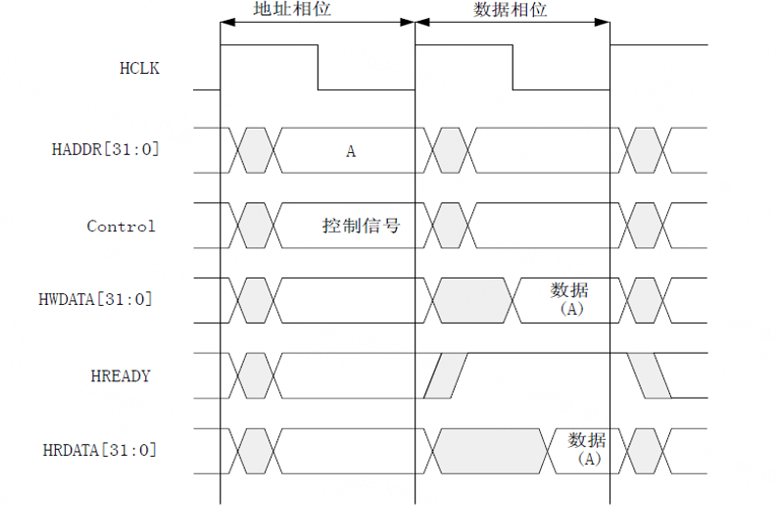

2.2.2 基本传输

一次完成的传输可分为两个相位:地址相位和数据相位。地址相位传输地址和control信号,而数据相位传输读写数据和response信号,下图 2.3表示一次AHB的基础传输:

图 2.3

若slave无法再单周期内处理完读写数据,可通过拉低并延长HREADY信号来对数据进行反压,当其拉高时,表示当前传输结束,过程如下图 2.4,结束状态由slave返回HRESP信号(OKAY、ERROR等)。

图 2.4

由于pipeline的存在导致连续传输时的phase会产生overlap(前次传输的datap hase与下次传输的address phase产生overlap),因此前次传输的data phase被延长时,下次传输的address phase也得跟着延长,如下图 2.5所示。

图 2.5

2.3 Control信号

AHB上的control信号共有五类,分别为

- HTRANS[1:0]:传输类型

- HBURST[2:0]:Burst类型

- HPORT[3:0]:protection信号

- HSIZE[2:0]:传输size

- HWRITE:传输方向

2.3.1 Transfer Type

AHB四种传输类型:

- IDLE:此时master不进行传输,而此时slave需在data phase回应OKAY。

- BUSY:在进行burst传输时,master若未准备好传输资料,则发出BUSY通知slave,同样的,slave回应OKAY。

- NONSEQ(Non-sequential):当前传输的address和control信号和上一笔传输无关(换句话说,就是一次burst传输的第一笔传输或者一次single传输)。

- SEQ(Sequential):当前传输的address和control信号和上一笔传输相同(也就是一次burst传输的非第一笔传输)。

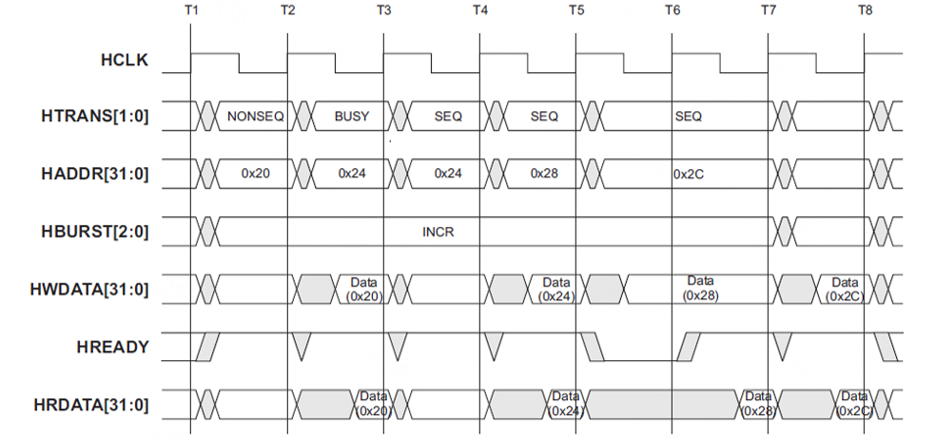

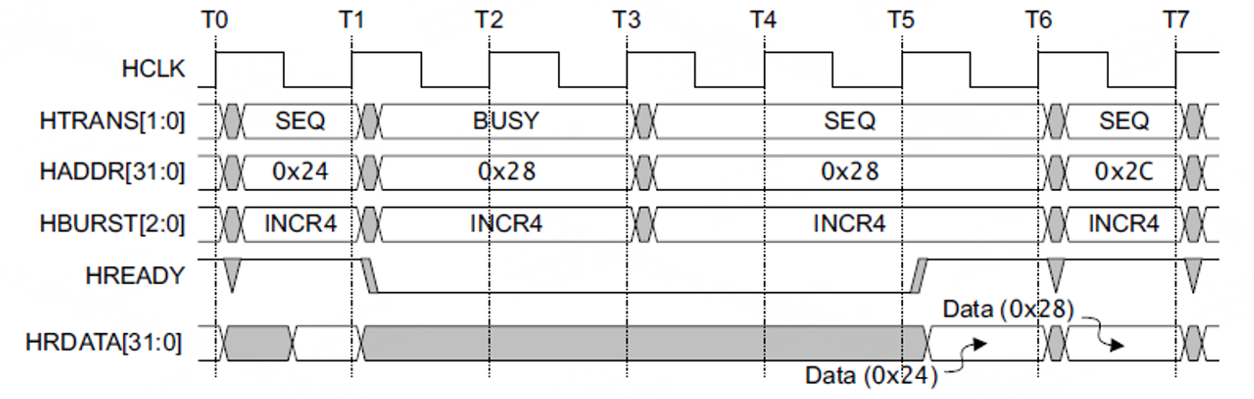

下图 2.6为一次传输的实例,从时序图中可以观察到

T1-T2:开始一次burst传输,

T2-T3:Master无法立刻执行第二笔传输,HTRANS发出一拍BUSY,slave返回一个OKAY;

T3-T4:Master进行第二笔传输;

T4-T5:Master进行第三笔传输;

T5-T6:Slave拉低HREADY表示对第三笔传输不能立刻响应,因此反压master,此时第四笔传输的address和control信号保持在地址路径中,第三笔的写数据保持在写数据通道中,第三笔的读数据不响应;

T6-T7:Slave拉高HREADY并响应第三笔传输;

T7-T8:Burst传输结束,slave响应第四笔传输。

图 2.6

2.3.2 Burst type

Burst传输是用来让AHB master发出address彼此相关的连续传输(control信号需相同)。burst传输的长度(传输的个数,beat),具体有八种,如下表:

| HBURST[2:0] | 类型 | 描述 |

| 000 | SINGLE | 单次传输 |

| 001 | INCR | 未指定长度的增量burst |

| 010 | WRAP4 | 4拍回环burst |

| 011 | INCR4 | 4拍增量burst |

| 100 | WRAP8 | 8拍回环burst |

| 101 | INCR8 | 8拍增量burst |

| 110 | WRAP16 | 16拍回环burst |

| 111 | INCR16 | 16拍增量burst |

其中,增量(incrementing)burst中,每一笔的传输address是上一笔传输的address加上传输size。而回环(wrapping)burst则是将memory切割成了(传输size*传输beat)大小的一个个memory边界,当传输address要跨过边界时,下一笔传输address会绕回到边界起点。例如,一次WRAP4且传输size为word(4 byte),那么自动将memory按照(4*4 byte)的边界进行划分,传输起始address若为0x34,则后三笔分别为0x38、0x3C以及回环到0x30(保证所有burst数据连续分布在一个回环块中),下图 2.7和图 2.8分别是WRAP4和INCR4的word size传输。

图 2.7

图 2.8

NOTE:

①INCR busrt可以是任意长度,但上限地址不可超过1 KB边界;

②所有burst传输必须将地址边界和传输size对齐。例如:word传输必须对齐word地址边界(即A[1:0]=00),half word传输对齐到half word边界(即A[0]=0)。

2.3.3 Transfer Direction

HWRITE拉高时,master在data phase将数据放在write data bus HWDATA[31:0]中,待下个clk有效沿让slave去sample data。HWRITE拉低时,slave会在data phase将数据放在read data bus HRDATA[31:0],待下个有效沿让master去sample data。

2.3.4 Transfer Size

传输size具体如下表:

| HSIZE[2:0] | Size | 描述 |

| 000 | 8 bits | 字节 |

| 001 | 16 bits | 半字 |

| 010 | 32 bits | 字 |

| ... | ... | ... |

2.3.5 Protection Control

HPROT[3:0]为master提供额外的protection information来表明当前传输是否是某些特定传输,具体如下表:

|

HPROT[3] cacheable |

HPROT[2] bufferable |

HPROT[1] privileged |

HPROT[0] data/opcode |

Description |

| - | - | - | 0 | Opcode fetch |

| - | - | - | 1 | Data access |

| - | - | 0 | - | User access |

| - | - | 1 | - | Privileged access |

| - | 0 | - | - | Not bufferable |

| - | 1 | - | - | Bufferable |

| 0 | - | - | - | Not cacheable |

| 1 | - | - | - | Cacheable |

2.4 Slave Response

在AHB协议中,slave除了可以用HREADY来延长等待周期,还可以使用HRESP[1:0]表示传输结束的状态。master发起传输后,只要slave被访问,那么就必须提供一个传输的response,该HRESP[1:0]具体如下表:

| HRESP[1:0] | 响应 | 描述 |

| 00 | OKAY | HREADY为高表示传输完成;HREADY为低时,OKAY响应用来扩展传输; |

| 00 | ERROR | 该响应代表发生了一个错误,ERROR响应需要双周期; |

| 01 | RETRY | 该响应表示传输未完成,master被授予访问bus时应当重新传输,RETRY响应需要双周期; |

| 01 | SPLIT | 该响应表示传输未完成,master应当在下一次被授予访问bus时继续传输,RETRY响应需要双周期; |

NOTE:

①仅OKAY响应在单周期给出,其他均为双周期;

之所以需要双周期,主要是由于AHB是pipeline的,相位间存在overlap,为了不影响下一次传输必须cancel下次传输,因此使用双周期对当前传输的数据挂起,对下笔传输的数据进行cancel;若是单周期的话,第A次传输收到RETRY的同时,第A+1次传输开始了,而此时的slave还在处理第A次传输,这样下去第A+1次以后的传输可能也都无法完成。

②对于RETRY和SPLIT:这两种状态均表示slave判断当前传输需要花费很多bus周期来完成,需要持续lock bus较长时间,为了避免对后续的传输产生影响,通过返回这两种状态进行bus所有权的重新分配,而两种状态的具体区别为:

* RETRY:返回后由arbiter重新对当前所有bus request的master进行优先级仲裁(包括返回RETRY的master);

* SPLIT:返回后由arbiter重新进行优先级仲裁(不包括返回SPLIT的master,因为此时该master的优先级被mask了,直到slave主动返回HSPLIT信 号给arbiter,由arbiter将对应的master优先级进行unmask后,待重新仲裁后根据优先级授予bus),若没有其他master进行bus request,则将bus access权移交给 dummy master进行IDLE传输。

从上述表述可以看出SPLIT相比RETRY可以在优先级重新仲裁时让较低优先级的master占据bus,但实现这种功能意味着更加复杂的硬件,首先arbiter需要观察HRESP信号(两种状态都需要),当收到SPLIT时,arbiter需要将对应的master的优先权mask(即更改优先权设计);slave同时需要记住返回master的id用于通知arbiter进行unmask,这个master的id可以从arbiter向slave发出的HMASTER信号查到,这个HMASTER是4 bit对应16个masters,而slave通知arbiter unmask的HSPILT信号是one-hot的16 bit。

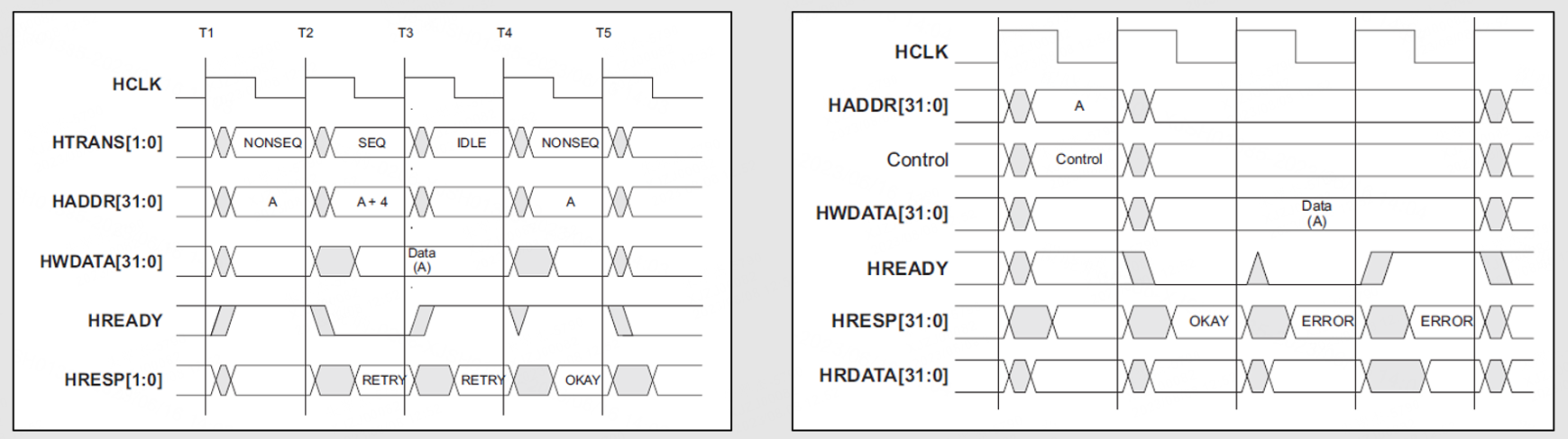

③双周期响应:如下图 2.9所示

若slave需要两个以上的周期去响应ERROR、RETRY和SPLIT时,额外的等待周期HREADY为低同时HRESP响应为OKAY;

双周期响应的第一拍,HRESP响应ERROR、RETRY和SPLIT,同时HREADY为低,响应的第二拍HRESP继续保持,HREADY置高结束传输;

对于SPLIT、RETRY响应接下来的传输必须取消并且在下一次传输开始前驱动HTRANS为IDLE;对于ERROR响应,master可以继续完成接下来的 传输。

图 2.9

2.5 Address Decoding

Address decoder提供HSELx给每个slave,这个decoder负责地址的简单译码(纯组合逻辑电路);HSELx拉高代表对应slave被选中,具体连接关系如下图 2.10。

图 2.10

NOTE:分配给单slave的最小地址空间为1 KB,因此master必须保证burst不能超过1 KB地址边界。

2.6 Aribitration

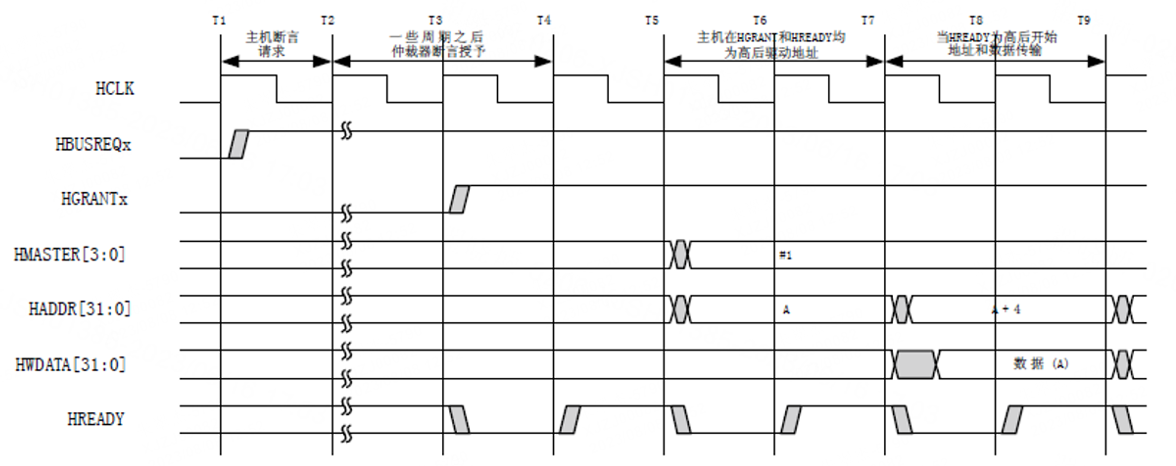

2.6.1 Bus的请求和授予(HBUSREQx and HGRANTx)

AHB只允许同一时间一个master获得bus access,因此多个master进行bus request时,在有效沿到来时,arbiter对所有request的master进行sample(通过每个master的HBUSREQx),仲裁算法有设计者自定义,arbiter将对应的master的HGRANTx信号拉高授予bus access,当HREADY也有效时(握手成功),master驱动address到地址bus上并在下个clk有效沿被slave所sample(进入data phase),具体如下图 2.11。

若传输为固定长度的burst,master在被授予bus access后可以不用继续request,待传输完成后重新request;若传输为不定长度的burst,master在被授予bus access后需要继续request bus,直到完成最后一笔传输。

图 2.11

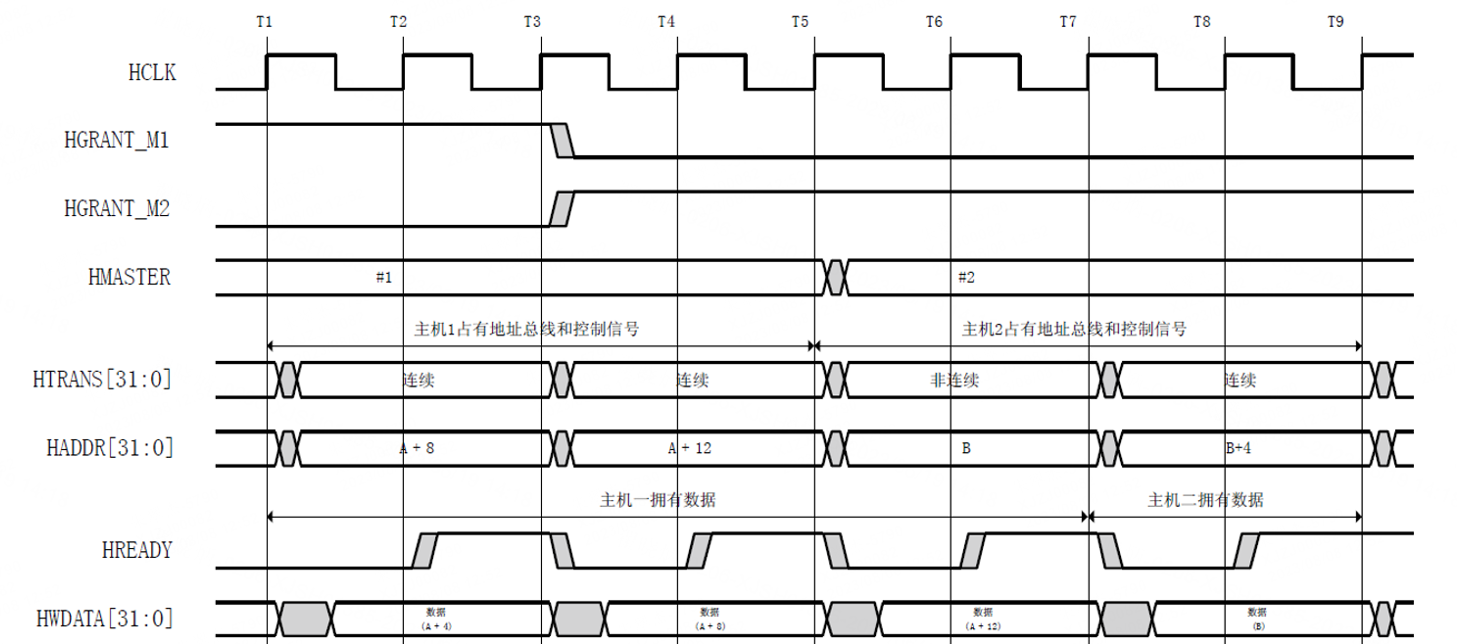

2.6.2 Bus handover

当arbiter向master assert了HGRANTx后,且HREADY为高,则slave在下个时钟沿进行sample;若HREADY信号一直拉低,则HGRANTx会一直保持等待与HREADY握手。若此时arbiter被更高优先级的master进行request,arbiter会更改HGRANTx信号,而bus access也会handover到新的bus上。

下图 2.12主要介绍了在bus handover时,master之间对address bus和data bus的控制以及延迟关系。

NOTE:当arbiter决定在burst结束后,进行bus handover时,arbiter会在倒数第二个传输的address被sample后,改变HGRANTx,所以新的HGRANTx将在最后一个传输的address一起被sample。

图 2.12

2.6.3 锁定传输HLOCKx

当master正进行固定长度的burst传输时,若出现更高优先级master的bus request,arbiter可以等待前一个burst传输完成后再进行bus handover;当然也可以直接中断前一个burst传输并bus handover到更高优先级的master,此时被中断的master需要重新bus request等待下次grant继续完成burst。

每个master的HLOCKx用来锁定当前传输不可被中断,master在向arbiter进行bus request时,同时拉高HLOCKx(保持address在发送前至少一个周期),锁定传输不在将bus release给其他master,直到master拉低HLOCKx。

Aribiter也会向slave assert HMASTLOCK信号,HMASTERLOCK信号与address和control信号时序相同,用于向slave指示当前为锁定传输。

2.6.4 Burst的提前终止

通常Arbiter在一个burst传输没有结束前不会改变bus授予,但协议中允许arbiter提前终止burst传输防止bus被占用时间过长;

如果master在burst传输中失去bus access,它必须重新进行bus request,并在获得bus access后继续发送剩余的传输(例如8 beat传输的3 beat完成后中断,再次获得bus access后必须以合法burst类型完成剩余的5笔,比如不定传输5 beat的INCR或在1 beat的SINGLE传输后接4 beat的INCR 4传输)。

2.7 AHB协议其他说明

- 对于定长的burst传输,协议禁止以BUSY类型结束传输;

- 对于不定长的burst传输,协议允许以BUSY类型结束传输;

- 在burst的等待状态传输过程中,master允许传输类型由BUSY变为SEQ。且更改为SEQ时,master必须保持HTRANSx不变,直到HREADY为高,如下图 2.13。

图 2.13

- 系统中存在default master和dummy master,当没有master进行bus request时,arbiter会默认将bus access给default master(有HBUSREx信号且此时master的HTRANS发出IDLE),default master通常是bus request频率较高的master,这种机制可以减少其request的bus handover的周期;

- 而dummy master非正常的master(没有接向arbiter的HBUSREQx信号),它被arbiter grant bus的情况有两种,一是所有master都收到slave的SPLIT响应而无法request bus时,二是当有master进行锁定传输时,且slave返回SPLIT(锁定传输规定当前burst无法被中断,而SPLIT使当前传输无法继续选中,产生冲突),此时bus access会给dummy master(只能被动接受),并且不断发送IDLE状态。

- Slave返回SPLIT后,对应的master不可再进行bus request access其他slave;而其他master可以access此slave,slave会记录后续access的master id并持续返回SPLIT,待当前传输完成后依次拉高之前记录的master对应的HSPLIT信号,待下个ckl有效沿来临时,sample address和control信号。

NOTE:

AHB系统有16个master,因此slave需要准备16组register去存储master id;

如果当slave处理SPLIT传输时,有master进行锁定传输到该slave,此时slave需要有限处理锁定传输(甚至要中断之前正在处理的传输),以免造 成整个bus被锁定传输给锁死。

- Slave返回RETRY后,在完成当前传输前不能被其他不同的master给access(通过软件层次预防)。

- 为了避免slave使用HREADY延长传输周期太长将bus锁死,协议规定每个slave需预设好最长的等待周期(建议16个周期)。