微处理器

参考自:吴宁,乔亚男.微型计算机原理与接口技术(第4版)[M].北京:清华大学出版社,2016-9:38-58.

8088/8086

硬件结构

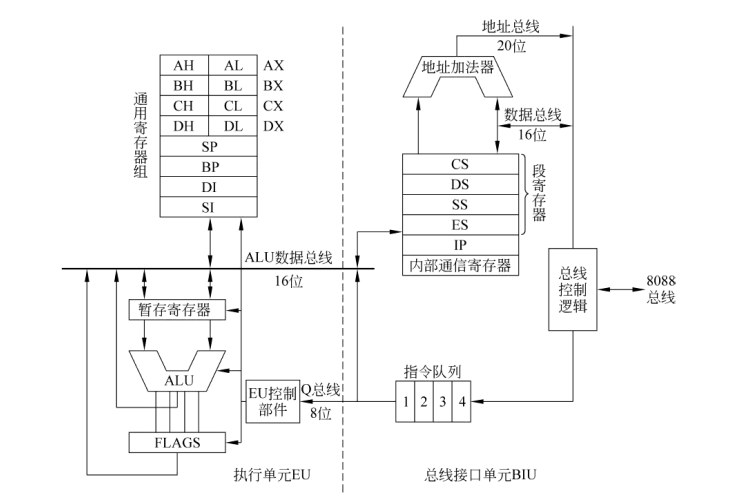

分执行单元(Execution Unit,EU)和总线接口单元(Bus Interface Unit,BIU)。取值周期和执行周期可独立执行。

分段管理,每段64K。AB20位,DB16位。指令队列长度8088有4字节,8086有6字节。

一般情况下,程序顺序执行,遇到跳转指令时,BIU就使指令队列复位,从新地址取出指令,并立即传给EU去执行。

寄存器

-

通用寄存器

-

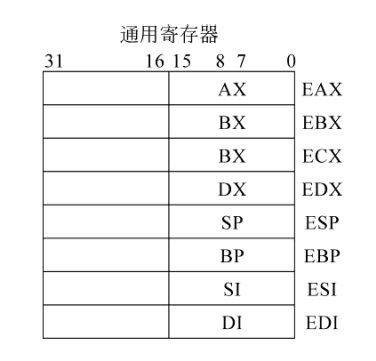

数据寄存器

- AX(Accumulator):ACC累加器。

- BX(Base):基址寄存器。常用来存放访问内存时的基地址。

- CX(Count):计数寄存器。在循环和串操作指令种用作计数器。

- DX(Data):数据寄存器。在寄存器间接寻址的I/O指令种存放I/O端口的地址。

双字长乘除法运算时,DX与AX合起来存放双字长数。DX高位、AX低位。

-

地址指针寄存器

- SP(Stack Pointer):堆栈指针寄存器。永远指向堆栈的栈顶。

- BP(Base Pointer):基址指针寄存器。

-

变址寄存器

- SI(Source Index):源变址寄存器。

- DI(Destination Index):目的变址寄存器。

-

-

段寄存器

- CS(Code Segment):代码段寄存器。

- SS(Stack Segment):堆栈段寄存器。

- DS(Data Segment):数据段寄存器。

- ES(Extra Segment):附加数据段寄存器。

-

控制寄存器

-

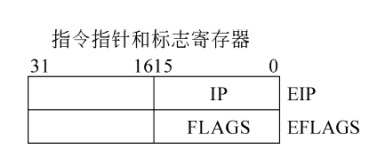

IP(Instruction Pointer):指令指针寄存器。

-

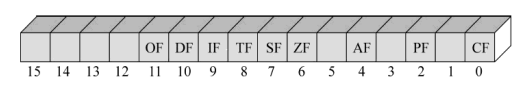

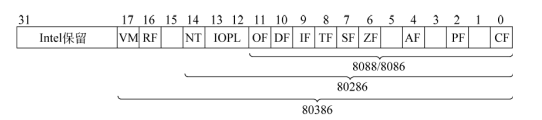

FLAGS:标志寄存器/程序状态字(PSW)。只用了9位。

- CF:进位标志位。

- PF:奇偶标志位。当运算结果的低8位中1的个数为偶数时PF=1。

- AF:辅助进位标志位。

- ZF:零标志位。

- SF:符号标志位。

- OF:溢出标志位。

- TF:陷阱标志位。

- IF:中断允许标志位。

- DF:方向标志位。在执行串操作指令时控制操作的方向。

-

段寄存器的使用

80386

硬件结构

全32位。CPU读写数据的宽度可在32位到16位之间切换。具有片内集成存储器管理部件MMU,可支持虚拟存储和特权保护。

有3种工作模式:实地址模式、保护模式、虚拟8086方式。

由于总线数据传送与总线地址形成可同时进行,所以80386的总线周期只有2个周期。

寄存器

通用寄存器

指令指针和标志寄存器

EFLAGS除了保留8088/8086的9个标志位外,新添4个标志位:

- IOPL(I/O Privilege Level):I/O特权级。此标志位用以指定I/O操作处于0~3特权层中的哪一层。

- NT(Nested Task):嵌套任务。为1表示当前执行的任务嵌套于另一任务中,执行完该任务后,要返回到原来的任务中去。

- VM(Virtual 8086 Mode):虚拟8086方式。为1处理器处于虚拟8086方式,否则为保护模式。

- RF(Resume Flag):恢复标志。

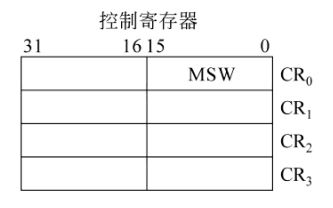

控制寄存器

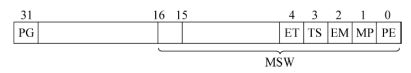

控制寄存器的作用是保存全局性的机器状态。其中CR0的格式如下:

- PE:允许保护位。进入保护位时为1;实方式时为0。

- MP:监视处理位。

- EM:仿真协处理位。

- TS:任务转换位。

- ET:协处理器类型位。

- PG:页式管理允许位。为1表示启用芯片内部的页式管理系统。

CR1由Intel公司保留、CR2存放引起页故障的线性地址、CR3存放当前任务的页目录基地址。

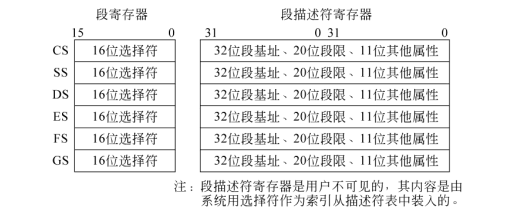

段寄存器和段描述寄存器

增加FS和GS主要是为了减轻对DS段和ES段的压力。

当用户将某一选择符装入一个段寄存器时,80386中的硬件会自动用段寄存器中的值作为索引从段描述符表中取出一个8字节的描述符,装入到与该段寄存器相应的64位描述符寄存器中。这个过程由80386CPU硬件自动完成。

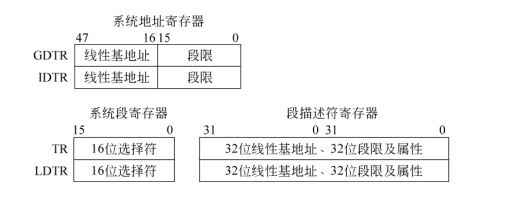

系统地址寄存器

- GDTR:全局描述符表寄存器。用于保存全局描述符表的32位基地址和全局描述符表的界限。

- IDTR:中断描述符表寄存器。用于保存中断描述符表的32位基地址和中断描述符表的界限。

- LDTR:局部描述符表寄存器。用于保存局部描述符表的选择符。一旦选择符放入LDTR,CPU会自动将选择符所指定的局部描述符装入64位的局部描述符寄存器中。

- TR:任务状态寄存器。用于保存任务状态段(TSS)的16位选择符。一旦选择符放入TR,CPU会自动将选择符所指定的任务描述符装入64位的任务描述符寄存器中。

调试寄存器

调试状态器为调试提供硬件支持。

- DR0~DR3:保存线性断点地址。

- DR4、DR5:备用寄存器。

- DR6:调试状态寄存器。通过该寄存器内容可以检测异常,并进入异常处理程序或禁止进入异常处理程序。

- DR7:调试控制寄存器。规定断点字段的长度、断点访问类型、允许断点和允许所选择的调试条件。

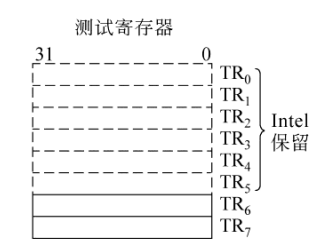

测试寄存器

测试寄存器用于控制对TLB中的RAM和CAM相连存储器的测试。

- TR6:测试控制寄存器。

- TR7:测试状态寄存器。用于保存测试结果的状态。