Physical Memory Layout

unavailable address for kernel

either because they map hardware devices’ I/O shared memory or because the corresponding page frames contain BIOS data

the address be reserved:

• Those falling in the unavailable physical address ranges

• Those containing the kernel’s code and initialized data structures

A page contained in a reserved page frame can never be dynamically assigned or swapped to disk.

Linux kernel's initialization of the Physical memory

mechine_specific_memory_setup()

builds the physical addresses map based on the physical addresses map provided by BIOS.(if map not provided, following the conservative default setup)

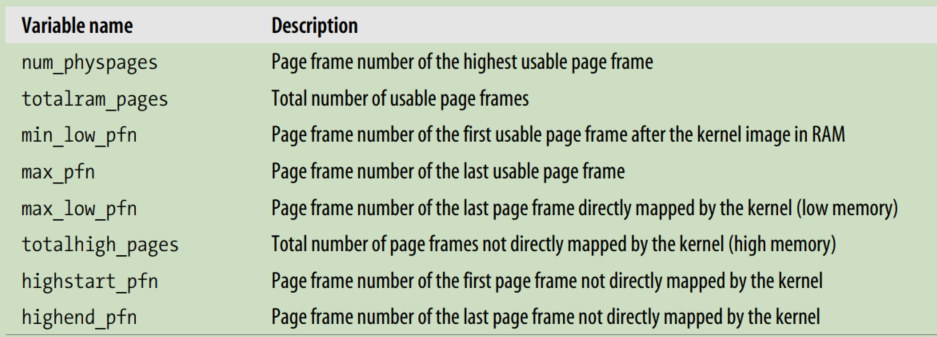

setup_memory()

it analyzes the table of physical memory regions and initializes a few variables that describe the kernel’s physical memory layout.

Process page Tables

The PAGE_OFFSET macro yields the linear address of the beganing of the kernel code(the separator of user address space and kernel address space).

Kernel Page Tables

The kernel maintains a set of page tables for its own use, rooted at a so-called master kernel Page Global Directory, which containes the reference model for the corresponding entries of the Page Global Directories of every regular process on its highest entries.

no page when in real mode --> provisional kernel Page Table --> Final Kernel Page Table

Provisional Page Tables

swapper_pg_dir -> the address of the PGD

PGD initialized during compliation --> startup_32() initialize PET

PGD

to allow to address the 8 MB of RAM easily both in real mode(without segment, linear address == logical address) and protected mode(use segment, linear address + seg_offset == logical address), the kernel first create a mapping from both the linear addresses 0x00000000 through 0x007fffff and the linear addresses 0xc0000000 through 0xc07fffff into the physical addresses 0x00000000 through 0x007fffff

startup_32()

also enable the paging unit, which means:

1.store swapeer_pg_dir into cr3

2.set PG flag of cr0

Final kernel Page Table

1.pagetable_init() to set up PTE

2.set cr3

3.__flush_tlb_all() to disable all TLB entries.

pagetable_init()

The actions performed by pagetable_init() depend on both the amount of RAM present and on the CPU model.

- less than 896 MB

- a.reset swapper_pg_dir

pgd = swapper_pg_dir + pgd_index(PAGE_OFFSET); - b.set new page flag

- c.clear the first 0-0x300 PTE in the provisional page tables.

-

between 896 MB and 4096 MB

dynamic remapping -

more than 4096 MB

with PAE support, mapping larger physical address.

Fix-Mapped Linear Address

at least 128 MB of linear addresses are always left available because the kernel uses them to implement noncontiguous memory allocation and fix-mapped linear addresses.

the kernel uses fix-mapped linear addresses instead of the const pointer variable.

a fix-mapped linear address can map any physical address.

点击查看代码

//op fixmap

set_fixmap(idx,phys);

set_fixmap_nocache(idx,phys);

fix_to_virt(idx);

Handling the Hardware Cache and the TLB

Handling the hardware cache

L1_CACHE_BYTES macro yields the size of a cache line in bytes.

To optimize the cache hit rate, the kernel considers the architecture in making the following decisions.

- The most frequently used fields of a data structure are placed at the low offset within the data structure, so they can be cached in the same line.

- When allocating a large set of data structures, the kernel tries to store each of them in memory in such a way that all cache lines are used uniformly.

the processor does the Cache Synchronization automically.

Handing the TLB

the fun provided by linux kernel

based on

the linux base macro op on tlb

base on

the assembly instructions op tlb provided by architecture.

Lazy TLB mode

to reduce the useless TLB flushing

When some CPUs start running a kernel thread, the kernel sets it into lazy TLB mode. When requests are issued to clear some TLB entries, each CPU in lazy TLB

mode does not flush the corresponding entries; however, the CPU remembers that its current process is running on a set of page tables whose TLB entries for the User Mode addresses are invalid. As soon as the CPU in lazy TLB mode switches to a regular process with a different set of page tables, the hardware automatically flushes the TLB entries, and the kernel sets the CPU back in non-lazy TLB mode.

- Understanding Addressing Chapter2 Chapter Memoryunderstanding addressing chapter2 chapter chapter2 chapter2目标chapter chapter2 chapter figure 20230814 chapter2 chapter 近邻 算法chapter2案例 addressing addressing continuous prediction feedback inspiration addressing reference pollution pre-addressed addressing messages enabled